CYII4SM6600-EVAL Cypress Semiconductor Corp, CYII4SM6600-EVAL Datasheet - Page 20

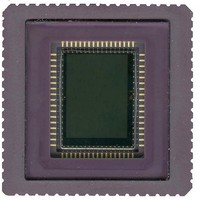

CYII4SM6600-EVAL

Manufacturer Part Number

CYII4SM6600-EVAL

Description

BOARD EVAL IMAGE SENS IBIS4-6600

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CYII4SC6600-EVAL.pdf

(34 pages)

Specifications of CYII4SM6600-EVAL

Sensor Type

CMOS Imaging, Monochrome

Sensing Range

6.6 Megapixel

Interface

SPI

Sensitivity

89 fps

Voltage - Supply

2.5 V ~ 3.3 V

Embedded

No

Utilized Ic / Part

IBIS4-6600

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

c.

If RESET_BLACK is set to 1, each line is reset before it is read

out (except for the row that is read out by the right pointer in NDR

Mode 2). This may be useful to obtain black pixels.

d.

The fast reset option (FAST_RESET = 1) might be useful in case

a mechanical camera shutter is used. The fast reset is done on

a row-by-row basis, not by a global reset. A global reset means

charging all the pixels at the same time, which may result in a

huge peak current. Therefore, the rows can be scanned rapidly

while the left and right shift registers are both controlled

identically, so that the reset lines over the pixel array are driven

from both sides. This reduces the reset (row blanking) time

(when FAST_RESET = 1 the smallest X-granularity can be

used). After the row blanking time, the row is reset and

Y_CLOCK can be asserted to reset the next row.

After a certain integration time, the read out can be done in a

similar method. The Y shift registers are again synchronized to

the first row. Both shift registers are driven identically, and all

rows and columns are scanned for (destructive) readout.

FAST_RESET = 1 puts the sequencer in such mode that the left

and right shift registers are both controlled identically.

e.

Bits FRAME_CAL_MODE and LINE_CAL_MODE define the

calibration mode of the output amplifier.

During every row-blanking period, a calibration is done of the

output amplifier. There are two calibration modes. The FAST

mode (= 0) can force a calibration in one cycle. However, it is not

Table 12. Granularity of X-Sequencer Clock and Corresponding Row Blanking Time (for NDR = 0).

h.

If BLACK is set to 1, the internal black signal is held high contin-

uously. As a result, the column amplifiers are disconnected from

the buses, and the buses are set to the voltage given by

DAC_DARK. The output of the amplifier equals the voltages from

the offset DACs.

i.

If RESET_ALL is set to 1, all the pixels are simultaneously put in

a 'reset' state. In this state, the pixels behave logarithmically with

light intensity. If this state is combined with one of the NDR

modes, the sensor can be used in a nonintegrating, logarithmic

mode with high dynamic range.

j.

After the internal X_SYNC is generated (start of the pixel readout

of a particular row), the PIXEL_VALID signal goes high. The

PIXEL_VALID signal goes low when the pixel counter reaches

the value loaded in the NROF_PIXEL register and an EOL pulse

is generated. Due to the fact that two pixels are addressed at

each internal clock cycle, the amount of pixels read out in one

row is 2*(NROF_PIXEL + 1).

Document Number: 001-02366 Rev. *G

Gran_x_seq_msb/lsb

Reset_black (Bit 3)

Fast_reset (Bit 4)

Output Amplifier Calibration (Bit 5 and 6)

Black (Bit 10)

Reset_all (Bit 11)

Nrof_pixels Register

00

01

10

11

X-Sequencer Clock

16 x sys_clock

2 x sys_clock

4 x sys_clock

8 x sys_clock

accurate and suffers from kTC noise, while the SLOW mode (=

1) can only make incremental adjustments and is noise free.

Approximately 200 or more "slow" calibrations have the same

effect as one "fast" calibration.

Different calibration modes can be set at the beginning of the

frame (FRAME_CAL_MODE bit) and for every subsequent row

that is read (LINE_CAL_MODE bit).

f.

For some applications, it might be necessary to use continuous

charging of the pixel columns instead of a precharge on every

row sample operation.

Setting bit CONT_CHARGE to 1 activates this function. The

resistor connected to pin CMD_COL is used to control the

current level on every pixel column.

g.

The system clock is divided several times on-chip.

The X-shift-register that controls the column/pixel readout, is

clocked by half the system clock rate. Odd and even pixel

columns are switched to two separate buses. In the output

amplifier, the pixel signals on the two buses can be combined to

one pixel stream at 40 MHz.

The clock that drives the X-sequencer can be a multiple of 2, 4,

8, or 16 times the system clock.

granularity of the X-sequencer clock and the corresponding row

blanking time (for NDR = 0). A row blanking time of 7.18 µs is the

baseline for almost all applications.

k.

After the internal YL_SYNC is generated (start of the frame

readout with Y_START), the line counter increases with each

Y_CLOCK pulse until it reaches the value loaded in the

NROF_LINES register and an EOF pulse is generated. In NDR

Mode 2, the line counter increments only every two Y_CLOCK

pulses and the EOF pulse shows up only after the readout of the

row indicated by the right shift register

INT_TIME Register

When the Y_START pulse is applied (start of the frame readout),

the sequencer generates the YL_SYNC pulse for the left Y-shift

register. This loads the left Y-shift register with the pointer loaded

in Y_REG register. At each Y_CLOCK pulse, the pointer shifts to

the next row and the integration time counter increases

(increment only every two Y_CLOCK pulses in NDR mode 2)

until it reaches the value loaded in the INT_TIME register. At that

moment, the YR_SYNC pulse for the right Y-shift register is

generated, which loads the right Y-shift register with the pointer

loaded in Y_REG register (shown in

1122 x TSYS_CLOCK

142 x TSYS_CLOCK

282 x TSYS_CLOCK

562 x TSYS_CLOCK

Row Blanking Time

Continuous Charge (Bit 7)

Internal Clock Granularities

Nrof_lines Register

IBIS4-6600 CYII4SM6600AB

Table 12

Row Blanking Time [µs]

Figure 20

lists the settings for the

14.05

28.05

3.55

7.05

on page 21).

Page 20 of 34

[+] Feedback