AT91SAM7X256B-CU Atmel, AT91SAM7X256B-CU Datasheet - Page 545

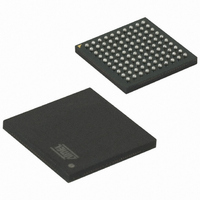

AT91SAM7X256B-CU

Manufacturer Part Number

AT91SAM7X256B-CU

Description

IC MCU 256KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7X256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, I2S, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Package

100TFBGA

Device Core

ARM7TDMI

Family Name

91S

Maximum Speed

55 MHz

On-chip Adc

8-chx10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 545 of 687

- Download datasheet (11Mb)

36.8.6

Name:

Access Type:

Any modification on one of the fields of the CANBR register must be done while CAN module is disabled.

To compute the different Bit Timings, please refer to the

• PHASE2: Phase 2 segment

This phase is used to compensate the edge phase error.

Warning: PHASE2 value must be different from 0.

• PHASE1: Phase 1 segment

This phase is used to compensate for edge phase error.

• PROPAG: Programming time segment

This part of the bit time is used to compensate for the physical delay times within the network.

• SJW: Re-synchronization jump width

To compensate for phase shifts between clock oscillators of different controllers on bus. The controller must re-synchronize

on any relevant signal edge of the current transmission. The synchronization jump width defines the maximum of clock

cycles a bit period may be shortened or lengthened by re-synchronization.

• BRP: Baudrate Prescaler.

This field allows user to program the period of the CAN system clock to determine the individual bit timing.

The BRP field must be within the range [1, 0x7F], i.e., BRP = 0 is not authorized.

• SMP: Sampling Mode

0 = The incoming bit stream is sampled once at sample point.

1 = The incoming bit stream is sampled three times with a period of a MCK clock period, centered on sample point.

SMP Sampling Mode is automatically disabled if BRP = 0.

6120H–ATARM–17-Feb-09

31

23

15

–

–

–

7

–

CAN Baudrate Register

t

t

t

t

t

PHS2

PHS1

PRS

SJW

CSC

=

=

=

=

=

30

22

14

CAN_BR

Read-write

–

–

6

t

t

(

CSC

CSC

t

t

BRP

CSC

CSC

×

×

×

×

+

(

(

1

(

(

PROPAG

SJW

PHASE2

PHASE1

)

⁄

PHASE1

MCK

+

29

21

13

–

5

1

)

+

+

+

1

1

1

SJW

)

)

)

AT91SAM7X512/256/128 Preliminary

28

20

12

–

4

Section 36.6.4.1 “CAN Bit Timing Configuration” on page

BRP

27

19

11

–

–

3

–

26

18

10

–

2

PROPAG

PHASE2

25

17

–

9

1

SMP

24

16

8

0

512.

545

Related parts for AT91SAM7X256B-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU 32BIT 128K 64LQFP

Manufacturer:

Atmel

Datasheet: