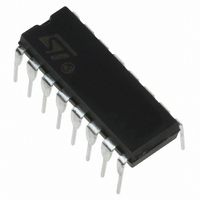

ST7FLITE09Y0B6 STMicroelectronics, ST7FLITE09Y0B6 Datasheet - Page 29

ST7FLITE09Y0B6

Manufacturer Part Number

ST7FLITE09Y0B6

Description

MCU 8BIT 1.5KB FLASH 128KB 16DIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST7FLITES2Y0B6.pdf

(124 pages)

Specifications of ST7FLITE09Y0B6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

SPI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

13

Program Memory Size

1.5KB (1.5K x 8)

Program Memory Type

FLASH

Eeprom Size

128 x 8

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

2.4 V ~ 5.5 V

Data Converters

A/D 5x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

16-DIP (0.300", 7.62mm)

Processor Series

ST7FLITE0x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

128 B

Interface Type

SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

13

Number Of Timers

2

Operating Supply Voltage

2.4 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7FLIT0-IND/USB, ST7FLIT2-COS/COM, ST7FLITE-SK/RAIS, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

For Use With

497-6250 - BOARD RGB COLOR CTRL STP04CM596497-5858 - EVAL BOARD PLAYBACK ST7FLITE497-5049 - KIT STARTER RAISONANCE ST7FLITE497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5632-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST7FLITE09Y0B6

Manufacturer:

Maestro

Quantity:

1 200

Company:

Part Number:

ST7FLITE09Y0B6

Manufacturer:

STMicroelectronics

Quantity:

135

8 INTERRUPTS

The ST7 core may be interrupted by one of two dif-

ferent methods: Maskable hardware interrupts as

listed in the Interrupt Mapping Table and a non-

maskable software interrupt (TRAP). The Interrupt

processing flowchart is shown in

The maskable interrupts must be enabled by

clearing the I bit in order to be serviced. However,

disabled interrupts may be latched and processed

when they are enabled (see external interrupts

subsection).

Note: After reset, all interrupts are disabled.

When an interrupt has to be serviced:

– Normal processing is suspended at the end of

– The PC, X, A and CC registers are saved onto

– The I bit of the CC register is set to prevent addi-

– The PC is then loaded with the interrupt vector of

The interrupt service routine should finish with the

IRET instruction which causes the contents of the

saved registers to be recovered from the stack.

Note: As a consequence of the IRET instruction,

the I bit is cleared and the main program resumes.

Priority Management

By default, a servicing interrupt cannot be inter-

rupted because the I bit is set by hardware enter-

ing in interrupt routine.

In the case when several interrupts are simultane-

ously pending, an hardware priority defines which

one will be serviced first (see the Interrupt Map-

ping Table).

Interrupts and Low Power Mode

All interrupts allow the processor to leave the

WAIT low power mode. Only external and specifi-

cally mentioned interrupts allow the processor to

leave the HALT low power mode (refer to the “Exit

from HALT” column in the Interrupt Mapping Ta-

ble).

the current instruction execution.

the stack.

tional interrupts.

the interrupt to service and the first instruction of

the interrupt service routine is fetched (refer to

the Interrupt Mapping Table for vector address-

es).

Figure

18.

8.1 NON MASKABLE SOFTWARE INTERRUPT

This interrupt is entered when the TRAP instruc-

tion is executed regardless of the state of the I bit.

It is serviced according to the flowchart in

18.

8.2 EXTERNAL INTERRUPTS

External interrupt vectors can be loaded into the

PC register if the corresponding external interrupt

occurred and if the I bit is cleared. These interrupts

allow the processor to leave the HALT low power

mode.

The external interrupt polarity is selected through

the miscellaneous register or interrupt register (if

available).

An external interrupt triggered on edge will be

latched and the interrupt request automatically

cleared upon entering the interrupt service routine.

Caution: The type of sensitivity defined in the Mis-

cellaneous or Interrupt register (if available) ap-

plies to the ei source. In case of a NANDed source

(as described in the I/O ports section), a low level

on an I/O pin, configured as input with interrupt,

masks the interrupt request even in case of rising-

edge sensitivity.

8.3 PERIPHERAL INTERRUPTS

Different peripheral interrupt flags in the status

register are able to cause an interrupt when they

are active if both:

– The I bit of the CC register is cleared.

– The corresponding enable bit is set in the control

If any of these two conditions is false, the interrupt

is latched and thus remains pending.

Clearing an interrupt request is done by:

– Writing “0” to the corresponding bit in the status

– Access to the status register while the flag is set

Note: The clearing sequence resets the internal

latch. A pending interrupt (that is, waiting for being

enabled) will therefore be lost if the clear se-

quence is executed.

register.

register or

followed by a read or write of an associated reg-

ister.

ST7LITE0xY0, ST7LITESxY0

Figure

29/124

1