EP4CGX15BF14C8N Altera, EP4CGX15BF14C8N Datasheet - Page 334

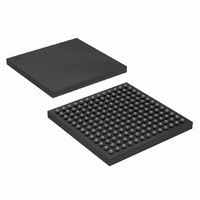

EP4CGX15BF14C8N

Manufacturer Part Number

EP4CGX15BF14C8N

Description

IC CYCLONE IV FPGA 15K 169FBGA

Manufacturer

Altera

Series

CYCLONE® IV GXr

Datasheets

1.EP4CGX15BN11C8N.pdf

(44 pages)

2.EP4CGX15BN11C8N.pdf

(14 pages)

3.EP4CGX15BN11C8N.pdf

(478 pages)

4.EP4CGX15BN11C8N.pdf

(10 pages)

Specifications of EP4CGX15BF14C8N

Number Of Logic Elements/cells

14400

Number Of Labs/clbs

900

Total Ram Bits

540000

Number Of I /o

72

Voltage - Supply

1.16 V ~ 1.24 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

169-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1475

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP4CGX15BF14C8N

Manufacturer:

ALTERA33

Quantity:

276

- EP4CGX15BN11C8N PDF datasheet

- EP4CGX15BN11C8N PDF datasheet #2

- EP4CGX15BN11C8N PDF datasheet #3

- EP4CGX15BN11C8N PDF datasheet #4

- Current page: 334 of 478

- Download datasheet (13Mb)

1–54

GIGE Mode

Cyclone IV Device Handbook, Volume 2

1

Figure 1–53. Compliance Pattern Transmission Support in PCI Express (PIPE) Mode

Reset Requirement

Cyclone IV GX devices meets the PCIe reset time requirement from device power up

to the link active state with the configuration schemes listed in

Table 1–18. Electrical Idle Inference Conditions

GIGE mode provides the transceiver channel datapath configuration for GbE

(specifically the 1000 Base-X physical layer device (PHY) standard) protocol

implementation. The Cyclone IV GX transceiver provides the PMA and the following

PCS functions as defined in the IEEE 802.3 specification for 1000 Base-X PHY:

■

■

■

Cyclone IV GX transceivers do not have built-in support for some PCS functions such

as auto-negotiation state machine, collision-detect, and carrier-sense. If required, you

must implement these functions in a user logic or external circuits.

Note to

(1) EP4CGX30 device in F484 package fulfills the PCIe reset time requirement using FPP configuration scheme with

8B/10B encoding and decoding

synchronization

upstream transmitter and local receiver clock frequency compensation (rate

matching)

configuration time of 41 ms.

EP4CGX30

EP4CGX110

EP4CGX150

EP4CGX15

EP4CGX22

EP4CGX50

EP4CGX75

Table

Device

tx_forcedispcompliance

1–18:

tx_ctrldetect[1..0]

(1)

tx_datain[15..0]

Fast passive parallel (FPP)

Configuration Scheme

Passive serial (PS)

/K28.5/D21.5/

B5BC

FPP

FPP

FPP

PS

PS

/K28.5/D10.2/

4ABC

Chapter 1: Cyclone IV Transceivers Architecture

01

/K28.5/D21.5/

B5BC

Configuration Time (ms)

© December 2010 Altera Corporation

Table

/K28.5/D10.2/

Transceiver Functional Modes

51

92

92

41

41

70

70

4ABC

1–17.

Related parts for EP4CGX15BF14C8N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: