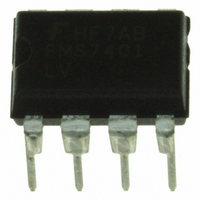

FMS7401LVN Fairchild Semiconductor, FMS7401LVN Datasheet - Page 48

FMS7401LVN

Manufacturer Part Number

FMS7401LVN

Description

IC CTRLR POWER DGTL EEPROM 8DIP

Manufacturer

Fairchild Semiconductor

Datasheet

1.FMS7401LVN.pdf

(81 pages)

Specifications of FMS7401LVN

Applications

Digital Power Controller

Core Processor

8-Bit

Program Memory Type

EEPROM (1 kB)

Ram Size

64 x 8

Number Of I /o

6

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 125°C

Mounting Type

Through Hole

Package / Case

8-DIP (0.300", 7.62mm)

Output Current

5 mA

Input Voltage

2.7 V to 3.6 V

Switching Frequency

2 MHz

Operating Temperature Range

- 40 C to + 125 C

Mounting Style

Through Hole

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Interface

-

Controller Series

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

FMS7401LVN_NL

FMS7401LVN_NL

FMS7401LVN_NL

Carry/Borrow (C)

The carry flag is set if the arithmetic logic unit (ALU) performs a carry or borrows during an arithmetic operation and by its

special inherent instructions—set carry (SC), load carry (LDC) and invert carry (INVC). The rotate instructions—rotate right/

left through carry (RRC/RLC)—operate with and through the carry bit to facilitate multiple-word shift operations. The RC,

SC, INVC, LDC and STC (store carry) instructions facilitate direct bit manipulation using the carry flag.

Half Carry (H)

The half carry flag indicates whether an overflow has taken place on the boundary between the two nibbles in the accumulator.

It is primarily used for Binary Coded Decimal (BCD) arithmetic calculation. The RC and SC instructions facilitate direct bit

manipulation of the half carry flag.

Zero (Z)

The zero flag is set if the result of an arithmetic, logic, or data manipulation operation is zero. Otherwise, the zero flag is

cleared.

Negative (N)

The result from an arithmetic, logic, or data manipulation operation is negative if the MSB is one, therefore setting the negative

flag. Otherwise, the negative flag is cleared.

Global Interrupt Mask (G)

The global interrupt bit (G) is a global mask that disables all maskable interrupt sources. If G is cleared, interrupts can become

pending but the operation of the core continues uninterrupted (even if the individual interrupts are enabled). However, if G is

set when an interrupt becomes pending the core will be interrupted and execute the appropriate interrupt service routine.

After a reset, G is defaulted to zero and can only be set by a software instruction. When an interrupt is recognized, G is auto-

matically cleared after the program counter value is stacked and the interrupt vector addressing the interrupt service routine is

fetched. Once the interrupt is serviced, a return-from-interrupt (RETI) instruction is normally executed to restore the program

counter to the value before the interrupt occurred. G is the restored to one after the return from interrupt is executed. Although

G can be set within an interrupt service routine, “nesting” interrupts in this way should only be done when there is a clear

understanding of latency and of the arbitration mechanism.

Table 23. Interrupt Priority Sequence

REV. 1.0.3 1/24/05

PRODUCT SPECIFICATION

Priority (5 highest, 1 lowest)

5

4

3

2

1

PWM Timer 1

Software

Timer 0

ADC

MIW

Interrupt

(EDGEI)

(TMRI0)

(TMRI1)

(ADCI)

(INTR)

FMS7401L

48