MC68MH360EM33L Freescale Semiconductor, MC68MH360EM33L Datasheet - Page 756

MC68MH360EM33L

Manufacturer Part Number

MC68MH360EM33L

Description

IC MPU QUICC ETHER 33MHZ 240FQFP

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68MH360ZP33L.pdf

(962 pages)

Specifications of MC68MH360EM33L

Processor Type

M683xx 32-Bit

Speed

33MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

240-FQFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68MH360EM33L

Manufacturer:

MOTOLOLA

Quantity:

319

Company:

Part Number:

MC68MH360EM33L

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 756 of 962

- Download datasheet (5Mb)

Freescale Semiconductor, Inc.

Applications

rupt acknowledge cycle was complete, which defeats the purpose of connecting the IPEND

pin to the BCLRI pin.)

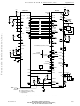

When the QUICC does not need the bus, it will assert the BG pin to the MC68EC040 con-

tinually, improving the MC68EC040 memory access performance.

9.4.1.6 BREAKPOINT GENERATION. In MC68EC040 companion mode, the QUICC can

be used to generate a breakpoint signal using its breakpoint address register. This register

will respond to QUICC or MC68EC040 accesses, but only the first access of an

MC68EC040 burst access.

The result of a breakpoint is the assertion of the BKPTO pin on the QUICC. In this applica-

tion, it was decided to route this output back to an interrupt input on the QUICC and generate

a nonmaskable interrupt to the MC68EC040. If the MC68EC040 encounters the breakpoint

trap, it will respond with a breakpoint acknowledge cycle. The QUICC does not recognize

this cycle and takes no action.

9.4.1.7 BUS MONITOR FUNCTION. In MC68EC040 companion mode, the QUICC will

monitor the bus for bus cycles that are not properly terminated. The cycles can originate

from the QUICC or the MC68EC040. If the MC68EC040 originates such a cycle and that

cycle times out without a TA or TEA occurring, the QUICC will assert TEA back to the

MC68EC040 to end the cycle.

9.4.1.8 SPURIOUS INTERRUPT MONITOR. In MC68EC040 companion mode, the QUICC

will watch for spurious interrupt cycles generated by the MC68EC040, but only on the inter-

rupt levels that the QUICC supports internally (e.g., the levels used by the SIM60 and the

level of the CPM). If such a condition occurs, TEA will be asserted by the QUICC.

9.4.1.9 SOFTWARE WATCHDOG. If desired, the MC68EC040 can program the QUICC

software watchdog to generate a level 7 interrupt or a system reset. In this application, the

software watchdog is configured in software to generate a reset so that the breakpoint logic

can use level 7 interrupts. No additional hardware is required because the connection

between the reset pins of the QUICC and the MC68EC040 is already made.

9.4.1.10 PERIODIC INTERVAL TIMER. If desired, the MC68EC040 can use the periodic

interval timer on the QUICC to generate a system interrupt, such as for a real-time kernel.

No additional hardware is required for this function.

9.4.1.11 MC68EC040 CACHING CONFIGURATION. The MC68EC040 can cache or not

cache data and can program memory as desired. However, it is strongly advisable not to

cache the data that is accessed by the QUICC serial channels because of the overhead

incurred every time a cached data area is written.

The MC68EC040 can decide to cache or not cache 16-byte portions of a bank of memory

on a dynamic basis by using a software technique summarized in 9.5 Selecting Cache

Modes on the MC68EC040.

9.4.1.12 MC68EC040 SNOOPING. The snooping function is not supported since only one

active processor exists in the system and the QUICC data buffers are not cached.

9-36

MC68360 USER’S MANUAL

MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Related parts for MC68MH360EM33L

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: