adc1613s NXP Semiconductors, adc1613s Datasheet

adc1613s

Related parts for adc1613s

adc1613s Summary of contents

Page 1

... The device also includes a programmable full-scale SPI to allow a flexible input voltage range from 1 V (p- (p-p). Excellent dynamic performance is maintained from the baseband to input frequencies of 170 MHz or more, making the ADC1613S ideal for use in communications, imaging, and medical applications. 2. Features and benefits SNR, 72.3 dBFS ...

Page 2

... HVQFN32R plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 7 × 7 × 0.8 mm HVQFN32R plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 7 × 7 × 0.8 mm All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Version SOT1152-1 SOT1152-1 SOT1152-1 SOT1152-1 © ...

Page 3

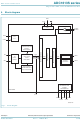

... PROCESSING OTR ADC CORE 16-BIT D15 to D0 PIPELINED CLOCK INPUT CYCLE CONTROL OTR All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface SDIO CS SPI SERIALIZER A 8-bit 8-bit 10-bit OUTPUT BUFFER A ...

Page 4

... I/O All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface 24 n.c. 23 DGND 22 DGND 21 VDDD ADC1613S 20 CMLN 19 CMLP 18 VDDD 17 DGND 001aam781 Description clock input ...

Page 5

... Thermal characteristics Parameter thermal resistance from junction to ambient thermal resistance from junction to case All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Description chip select out-of-range information digital power supply 1.8 V ...

Page 6

... Power-down mode Standby mode peak-to-peak peak track mode track mode track mode track mode peak-to-peak All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Min Typ Max 2.85 3.0 3.4 1.65 1.8 1.95 - ...

Page 7

... DC-coupled; output AC-coupled DC-coupled; output AC-coupled DC-coupled; output AC-coupled DC-coupled; output AC-coupled differential; input guaranteed no missing codes All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Min Typ Max - 0.5V - DDA - 4 - 0.5 ...

Page 8

... V, T DDD(1V8) amb = 1 DDA DDD(1V8) i(INP) All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Min Typ ± 0.5 - −54 - − −1 dBFS; internal reference mode; 100 Ω differential ...

Page 9

... ADC1613S125 Unit Typ Max Min Typ Max dBc dBc dBc dBc dBc dBc dBc dBc dBc ...

Page 10

... Typ Max 307 - 850 250 - 283 0 0 °C. Minimum and maximum values are across the full temperature range T amb ADC1613S105 ADC1613S125 Unit Min Typ Max Min Typ Max - dBc - dBc - dBc - dBc ...

Page 11

... ADC1613S_SER Product data sheet = 25 °C Eye diagram receiver common-mode Eye diagram receiver common-mode All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Figure 3 and Figure 4. Test conditions 005aaa088 005aaa089 © ...

Page 12

... CS w(SCLK) h SCLK SDIO W1 W0 R/W SPI timing All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Min Typ - ° ...

Page 13

... NXP Semiconductors 11. Application information 11.1 Analog inputs 11.1.1 Input stage description The analog input of the ADC1613S supports a differential or a single-ended input drive. Optimal performance is achieved using differential inputs with the common-mode input voltage (V The full-scale analog input voltage range is configurable between 1 V (p-p) and 2 V (p-p) ...

Page 14

... Figure 8 would be suitable for a baseband application. ADT1-1WT 100 nF analog input 100 nF Single transformer configuration All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface R INP C R INM 005aaa073 Capacitance (pF ...

Page 15

... Fig 9. 11.2 System reference and power management 11.2.1 Internal/external reference The ADC1613S has a stable and accurate built-in internal reference voltage to adjust the ADC full-scale. This reference voltage can be set internally via SPI or with pins VREF an SENSE (see control bits INTREF[2:0] (when bit INTREF_EN = logic 1; see ...

Page 16

... Figure 14 illustrate how to connect the SENSE and VREF pins to select the All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface BANDGAP REFERENCE EXT_ref ADC CORE SENSE pin VREF pin ...

Page 17

... Reference modes Level 0 dB −1 dB −2 dB −3 dB −4 dB −5 dB −6 dB not used All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface VREF 330 pF REFERENCE EQUIVALENT SCHEMATIC SENSE VREF 0.1 μF V REFERENCE ...

Page 18

... Biasing The common-mode input voltage (V 0.5V DDA 11.3 Clock input 11.3.1 Drive modes The ADC1613S can be driven differentially (LVPECL). It can also be driven by a single-ended LVCMOS signal connected to pin CLKP (CLKM should be connected to ground via a capacitor). a. Rising edge LVCMOS Fig 16. LVCMOS single-ended clock input ADC1613S_SER ...

Page 19

... ESD CLKP CLKM V = common-mode voltage of the differential input stage. cm(clk) All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Sine clock input b. Sine clock input (with transformer) CLKP CLKM 005aaa172 Figure 18 ...

Page 20

... Clock input divider The ADC1613S contains an input clock divider that divides the incoming clock by a factor of 2 (when bit CLKDIV2_SEL = logic 1; see deliver a higher clock frequency with better jitter performance, leading to a better SNR result once acquisition has been performed. ...

Page 21

... L LANES FRAME TO SCRAMBLER F octets OCTETS × L (F) octets L octets All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series 10 nF RECEIVER 100 Ω 005aaa187 ALIGNMENT 8-bit/ CHARACTER SER 10-bit GENERATOR TX CONTROLLER 005aaa198 © NXP B.V. 2011. All rights reserved. ...

Page 22

... All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface LANE_MODE[1:0] 00 SCR 8-bit/ 10-bit ...

Page 23

... NXP Semiconductors 11.6 Serial Peripheral Interface (SPI) 11.6.1 Register description The ADC1613S serial interface is a synchronous serial communications port allowing easy interfacing with many industry microprocessors. It provides access to the registers that control the operation of the chip in both read and write modes. This interface is configured as a 3-wire type (SDIO as bidirectional pin). ...

Page 24

... ADC1613S_SER Product data sheet Instruction bytes All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface Register N (data) Register (data) D4 ...

Page 25

Channel control Table 17. Register allocation map [1] Address Register name Access (hex) Bit 7 ADC control register 0003 SPI control R/W - 0005 Reset and R/W SW_RST Operating modes 0006 Clock R/W - 0008 Vref R/W - 0013 ...

Page 26

Table 17. Register allocation map …continued [1] Address Register name Access (hex) Bit 7 080A Ser_ScramblerB R/W 080B Ser_PRBS_Ctrl R/W 0 0820 Cfg_0_DID R 0821 Cfg_1_BID R/W* 0 0822 Cfg_3_SCR_L R/W* SCR 0823 Cfg_4_F R/W* 0 0824 Cfg_5_K R/W* 0 ...

Page 27

... All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series © NXP B.V. 2011. All rights reserved ...

Page 28

... All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface +31 LSB ... 0 ... −32 LSB © NXP B.V. 2011. All rights reserved. ...

Page 29

... Single-ended mode - 1 not used - LSB are swapped to MSB at the scrambler input: 0 disable 1 enable All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 30

... PRBS-7 01 PRBS-7 10 PRBS-23 11 PRBS-31 Access Value Description R 11101101 defines the device (= link) identification number All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 31

... Value Description - 000 not used R/W 01111 defines the total number of bits per sample, minus 1 All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 32

... PRBS mode: lane output is the PRBS generator (PRBS type is defined with “PRBS_TYPE[1:0]” (Ser_PRBS_Ctrl register not used All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 33

... R/W ADC power-down control: 0 ADC is operational 1 ADC is in Power-down mode All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 34

... 7.1 4.05 0.55 0.10 7.0 4.00 0.65 4.55 4.55 0.50 0.05 6.9 3.95 0.45 0.00 References JEDEC JEITA - - - - - - All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface A detail 0.1 0.05 0.08 0.1 European projection SOT1152 sot1152-1_po Issue date ...

Page 35

... OuT-of-Range Pseudo-Random Binary Sequence Spurious-Free Dynamic Range Signal-to-Noise Ratio Serial Peripheral Interface Transmitter All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface © NXP B.V. 2011. All rights reserved ...

Page 36

... NXP Semiconductors 14. Revision history Table 48. Revision history Document ID ADC1613S_SER v.1 ADC1613S_SER Product data sheet Release date Data sheet status 20110314 Product data sheet All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series Single 16-bit ADC; serial JESD204A interface ...

Page 37

... Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities. All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series © NXP B.V. 2011. All rights reserved ...

Page 38

... Trademarks Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners. http://www.nxp.com salesaddresses@nxp.com All information provided in this document is subject to legal disclaimers. Rev. 1 — 14 March 2011 ADC1613S series © NXP B.V. 2011. All rights reserved ...

Page 39

... Please be aware that important notices concerning this document and the product(s) described herein, have been included in section ‘Legal information’. © NXP B.V. 2011. For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com ADC1613S series All rights reserved. Date of release: 14 March 2011 Document identifier: ADC1613S_SER ...