uda1324ts NXP Semiconductors, uda1324ts Datasheet - Page 4

uda1324ts

Manufacturer Part Number

uda1324ts

Description

Ultra Low-voltage Stereo Filter Dac

Manufacturer

NXP Semiconductors

Datasheet

1.UDA1324TS.pdf

(20 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UDA1324TS

Manufacturer:

PHILIPS

Quantity:

2 680

Company:

Part Number:

uda1324ts/N1

Manufacturer:

PHILIPS

Quantity:

16 529

Philips Semiconductors

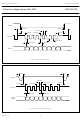

PINNING

2001 Mar 27

handbook, halfpage

BCK

WS

DATAI

V

V

SYSCLK

APPSEL

APPL3

APPL2

APPL1

APPL0

V

V

VOUTL

V

VOUTR

SYMBOL

DDD

SSD

ref(DAC)

DDA

SSA

Ultra low-voltage stereo filter DAC

SYSCLK

APPSEL

APPL3

DATAI

V DDD

V SSD

PIN

BCK

10

11

12

13

14

15

16

WS

Fig.2 Pin configuration.

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

bit clock input

word select input

data input

digital supply voltage

digital ground

system clock input: 256f

and 512f

application mode select input

application input pin 3

application input pin 2

application input pin 1

application input pin 0

DAC reference voltage

analog supply voltage for DAC

left channel output

analog ground for DAC

right channel output

UDA1324TS

MBK769

s

DESCRIPTION

16

15

14

13

12

11

10

9

VOUTR

V SSA

VOUTL

V DDA

V ref(DAC)

APPL0

APPL1

APPL2

s

, 384f

s

4

FUNCTIONAL DESCRIPTION

System clock

The UDA1324TS operates in the slave mode only.

Therefore, in all applications the system devices must

provide the system clock. The system frequency (f

selectable and depends on the application mode.

The options are: 256f

and 256f

clock must be locked in frequency to the digital interface

input signals.

The UDA1324TS supports sampling frequencies (f

8 to 48 kHz.

Application modes

The application mode can be set with the three-level

pin APPSEL (see Table 1):

Table 1 Selecting application mode and system clock

The function of an application input pin (active HIGH)

depends on the application mode (see Table 2).

Table 2 Functions of application input pins

For example, in the static pin mode the output signal can

be soft muted by setting pin APPL0 to HIGH.

De-emphasis can be switched on for 44.1 kHz by setting

pin APPL1 to HIGH; setting pin APPL1 to LOW will disable

de-emphasis.

VOLTAGE ON

PIN APPSEL

L3 mode

Static pin mode with f

Static pin mode with f

0.5V

APPL0

APPL1

APPL2

APPL3

V

V

PIN

DDD

SSD

s

DDD

frequency via pin APPSEL

or 384f

s

for the static pin mode. The system

static pin mode

L3CLOCK

L3 MODE

s

L3MODE

, 384f

L3 mode

L3DATA

MODE

TEST

sys

sys

= 384f

= 256f

s

and 512f

FUNCTION

s

s

.

UDA1324TS

256f

Product specification

STATIC PIN MODE

s

for the L3 mode

s

, 384f

DEEM

MUTE

384f

256f

SF0

SF1

f

sys

s

s

s

or 512f

sys

s

) from

) is

s