DM74S74N Fairchild Semiconductor, DM74S74N Datasheet

DM74S74N

Specifications of DM74S74N

74S74N

Available stocks

Related parts for DM74S74N

DM74S74N Summary of contents

Page 1

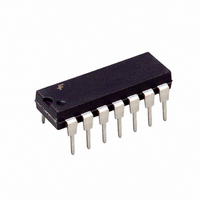

... Package Number DM74S74M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow DM74S74N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code. ...

Page 2

Absolute Maximum Ratings Supply Voltage Input Voltage Operating Free Air Temperature Range Storage Temperature Range Recommended Operating Conditions Symbol Parameter V Supply Voltage CC V HIGH Level Input Voltage IH V LOW Level Input Voltage IL I HIGH Level Output ...

Page 3

Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted) Symbol Parameter V Input Clamp Voltage HIGH Level V OH Output Voltage V V LOW Level V OL Output Voltage V I Input Current @ ...

Page 4

Physical Dimensions inches (millimeters) unless otherwise noted 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow www.fairchildsemi.com Package Number M14A 4 ...

Page 5

Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right ...