CD4019BCN Fairchild Semiconductor, CD4019BCN Datasheet

CD4019BCN

Specifications of CD4019BCN

4019B

CD4019

Available stocks

Related parts for CD4019BCN

CD4019BCN Summary of contents

Page 1

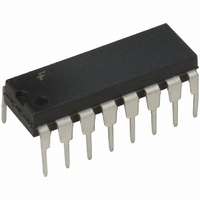

... Package Number CD4019BCM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow CD4019BCN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code. ...

Page 2

Schematic Diagram Schematic diagram for identical stages www.fairchildsemi.com 2 ...

Page 3

Absolute Maximum Ratings (Note 2) Supply Voltage ( Input Voltage ( Storage Temperature Range ( Power Dissipation ( Dual-In-Line Small Outline Lead Temperature ( (Soldering, 10 seconds) ...

Page 4

AC Electrical Characteristics pF 200k, unless otherwise specified Symbol Parameter t , Propagation Delay, PHL t Input to Output PLH t HIGH-to-LOW Level THL Transition Time t LOW-to-HIGH Level TLH Transition ...

Page 5

Physical Dimensions inches (millimeters) unless otherwise noted 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A 5 www.fairchildsemi.com ...

Page 6

Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right ...