tda8026 NXP Semiconductors, tda8026 Datasheet

tda8026

Available stocks

Related parts for tda8026

tda8026 Summary of contents

Page 1

... Rev. 1 — 9 March 2010 1. General description The TDA8026 is a cost-effective, analog interface for addressing multiple smart card slots in a Point Of Sales (POS) terminal. It can address up to two main cards (synchronous or asynchronous smart cards supported) and up to four Security Access Modules (SAMs). ...

Page 2

... Rev. 1 — 9 March 2010 Multiple smart card slot interface IC Min Typ [1] 2.7 - [1] 5. 300 - 3.7 ; pins CLKIN1 [ 210 clk(ext) [ mA; CC(2) 1 clk(ext) TDA8026 and Max Unit 5 450 260 mA 3 © NXP B.V. 2010. All rights reserved ...

Page 3

... CC(3) CC(4) CC(5) total sequence +85 C amb Description plastic thin fine-pitch ball grid array package; 64 balls All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC and Min Typ Max [5] 4.75 5 5.25 2. ...

Page 4

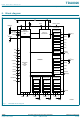

... INTAUXN INTERFACE C4 I/OUC1 CONTROL C5 I/OUC2 C3 CLKIN1 B3 CLKIN2 H1 SPRES A3 TESTMODE H7 INHIB D1 STAP5 STAP4 Fig 1. TDA8026 Block diagram TDA8026_1 Product data sheet V DD(INTREGD) GNDP POWER STEP UP UNIT CONVERTER TDA8026 AND UNIT SEQUENCER SEQUENCER V CC GENERATOR GENERATOR RST BUFFER RST BUFFER CLK BUFFER ...

Page 5

... A TST2 B STAP3 C STAP4 D STAP5 ( (1) H SPRES PRES [1] The numbers in subscript and between brackets “ [2] The ball positions are those when the TDA8026 is viewed from the top. TDA8026_1 Product data sheet ball A1 index area TDA8026 pin confi ...

Page 6

... C7 CC(3) All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC auxiliary contact reader front end not connected: connect INTAUXN pad to supply voltage V auxiliary contact reader front end connected: connect INTAUXN pad to an external 10 k pull-up resistor ...

Page 7

... ground value. DD(INTF) value. CC(n) All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC [5] [5] [5] threshold used: connect pin PORADJ using an external resistor bridge threshold not used: connect to V DD(INTF) ; position C3 CLK ...

Page 8

... V SHDWN = 1 SHUTDOWN (1) Active mode; DC-to-DC converter is ON. (2) V Fig 3. 8.2 Power modes Three power modes are available for the TDA8026. These are: • Standby mode • Active mode with a clock-stop sub-mode • Shutdown mode TDA8026_1 ...

Page 9

... Shutdown mode Shutdown mode is the very low power consumption mode, typically 25 A. The TDA8026 enters this mode when the SDWNN pin is driven LOW. Only presence monitoring on card slot 1 remains enabled. When card insertion or removal is detected on card slot 1, an interrupt signal (IRQN) is sent to the microcontroller ...

Page 10

... When the SDWNN pin is HIGH, the IRQN pin is set to HIGH and the analog module is powered-up. A full power-up sequence is executed by the TDA8026 4. When the TDA8026 is ready, the IRQN pin is set to LOW 5. The microcontroller detects the device interrupt using the IRQN pin and services it which resets pin IRQN to HIGH Fig 5 ...

Page 11

... The supervisors control the internal regulated supply voltage (V ensure problem-free operation of the TDA8026. This block controls: • • the microcontroller interface supply voltage (V PORADJ pin (V When an alarm occurs, the internal digital controller resets the TDA8026 DD(INTREGD) ALARMN (internal signal) Fig 7. TDA8026_1 Product data sheet ...

Page 12

... The alarm is reset and the TDA8026 leaves reset mode 8 ms after V above their respective Thus reset mode, the TDA8026 is inactive and does not respond to any external command lines. TDA8026_1 Product data sheet V DD(INTF hys V th ...

Page 13

... NXP Semiconductors 2 8.4 I C-bus description Remark: Refer to the I 2 The I C-bus interface in the TDA8026 (100 kHz) or Fast mode (400 kHz). In addition, it integrates shift register functions, shift timing generation and slave address recognition. 2 8.4.1 I C-bus protocol 2 The I C-bus protocol is based on bidirectional, 2-line communication between ICs or modules ...

Page 14

... Bank 1 page selection is performed when the configuration byte (CSb[7:0]) is written to the high address representing bank 0 based on the A0 pin value. Using pin A0, two TDA8026s can be used in parallel based on the selection made to the address selection pin A0. Pin A0 is externally hardwired to the pins V ...

Page 15

... NXP Semiconductors 8.5 Banks and registers The device registers enable the microcontroller to control the TDA8026. These registers are defined as banks: • Bank 0 register is a read/write register which enables selection of the required card slot number and access to the corresponding registers Bank 1 registers. In addition, Bank 0 is used to write information about the interrupt status and the product version ...

Page 16

Register overview Table 7. Register overview Page number/ Register R/W Bit definition register name Bit 7 Subaddress [1] (Hex) Bank 0: Card slot selection, product version and interrupt registers (see -/48h CSb R/W Bank 1: Card slot registers (see ...

Page 17

Table 7. Register overview …continued Page number/ Register R/W Bit definition register name Bit 7 Subaddress [1] (Hex) Slot 4 04h/40h Register0 R ACTIVE 04h/40h Register0 W VCC1V8 [3] [2] 04h/42h Register1 R/W - [4] 04h/42h Register1 R/W [5] 04h/42h ...

Page 18

... NXP Semiconductors 8.5.2 Bank 0 register description The device registers enable the microcontroller to control the TDA8026. The registers are organized in bank pages to ensure compatibility with the TDA8023. Bank 0 write register enables selection of the card slot number and access to the corresponding registers in bank 1. The card slot registers in bank 1 are accessed using the confi ...

Page 19

... CLKIN1 and CLKIN2. All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 Multiple smart card slot interface osc int is the internal oscillator frequency) osc(int) [1] frequency clk(ext) TDA8026 © NXP B.V. 2010. All rights reserved ...

Page 20

... SUPL and PROT bits are logic 0 and the PRES bit is logic 1) 0 set to logic 0: starts the deactivation sequence All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC = 1.8 V; ignores the 5V/3VN bit logic state CC(n) is set using the 5V/3VN bit CC(n) ...

Page 21

... Rev. 1 — 9 March 2010 Multiple smart card slot interface [2] C4(1) CLKPD[1:0] R/W R/W R/W [1] [2] - CLKPD[1:0] R/W R/W R/W Table 16 on page 23 D[7:0] R/W Table 18 on page 23 C[15:8] R/W Table 20 on page 23 C[7:0] R/W is LOW (n) pin (1) pin (1) TDA8026 1 0 [3] CLKDIV[1:0] R/W R/W [3] CLKDIV[1:0 ] R/W R/W is set to HIGH (n) pin (1) pin (1) © NXP B.V. 2010. All rights reserved ...

Page 22

... CLK clk(ext) clk(ext pin CLK clk(ext pin CLK clk(ext pin CLK clk(ext pin CLK clk(ext D[7:0] R/W TDA8026 set using (clk) on pin CLK (1) (2) ( pin CLK (2) (1) (2) (1) ( © NXP B.V. 2010. All rights reserved. ...

Page 23

... This value is applied to all slots. The reset value is 74h. See to reset counters” on page All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC Section 8.9 “Answer to reset counters” on page 4 3 ...

Page 24

... Multiple smart card slot interface PROT SUPL CLKSW REG[1:0] PDWN 5V/3VN Table 23 for more detailed f 2 osc int is the internal oscillator frequency) osc(int) clk(ext) TDA8026 1 0 [1] - STAP R R WARM START W W © NXP B.V. 2010. All rights reserved ...

Page 25

... PRES bit is logic 1, the activation sequence and cold reset procedure are started 0 set to logic 0: deactivation sequence starts All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC = 1.8 V; ignores the 5V/3VN bit logic state CC(n) is set using the 5V/3VN bit CC(n) ...

Page 26

... RSTIN is controlled by the hardware (ATR management) 0 set to logic 0: RST - - reserved All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 Multiple smart card slot interface [1] [2] - CLKPD[1:0] R/W R/W R/W D[7:0] R/W C[15:8] R/W C[7:0] R/W is set LOW (n) TDA8026 1 0 [3] CLKDIV[1:0 ] R/W R/W is set to HIGH (n) © NXP B.V. 2010. All rights reserved ...

Page 27

... All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 Multiple smart card slot interface IC …continued f osc int is the internal oscillator frequency) osc(int D[7:0] R/W Section 8.9 “Answer to reset counters” on page TDA8026 set using (clk © NXP B.V. 2010. All rights reserved ...

Page 28

... Selection of asynchronous or synchronous mode When the activation sequence starts, the selected card slot on the TDA8026 uses the RSTIN bit value to configure itself for use with asynchronous or synchronous cards. If the RSTIN bit is set to logic 1 at the activation sequence start (the START bit changes from LOW to HIGH), the TDA8026 will manage asynchronous cards ...

Page 29

... Synchronous mode card clock settings CLKDIV[1:0] bit CLKPD[1:0] bit Card clock (CLK [1] - All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC CLKPD[1:0] bit Card clock (CLK clk(ext clk(ext clk(ext) ...

Page 30

... Description PV[7:0] reading this register returns the product version. The MSB nibble is C (commercial product) and the LSB nibble is 2 (release number) All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface PV[7:0] ...

Page 31

... IO_SR[1:0] card slot 1 I/O slew rate selection for more detailed information. All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC © NXP B.V. 2010. All rights reserved ...

Page 32

... This causes the IRQN line to be driven LOW and the Bank 1 Register 0 PROT bit is set to logic 1. The DC-to-DC converter is deactivated when the TDA8026 is in shutdown mode. The card slots can be directly supplied by the V 5 ...

Page 33

... GNDS depending of the card slot. (n) , see Figure due to integrated 10 k pull-ups for CC( and the RST pin is enabled. The RST 4 act (n) which leads to a time interval (typical). and TDA8026 10 (n) © NXP B.V. 2010. All rights reserved ...

Page 34

... the time that V deact All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC high frequency are driven with a low-impedance switch ...

Page 35

... Fig 11. Deactivation sequence In Figure 11 converter is still active. 8.9 Answer to reset counters Each TDA8026 card slot has its own sequencer. The sequencer controls the activation and deactivation sequences. In addition to these sequencers, there are two Answer To Reset (ATR) counters: • ATR dedicated to card slot 1 • ...

Page 36

... Table 12 on page 20, Table 22 on page 24 All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC is enabled and CLK (n) 34). Pin RST (n) during the first 200 clock cycles are ...

Page 37

... The (n) CC(n) (low) Rise and fall time (ns signal can be configured with the two Table 39 on page 37: Fall time (ns TDA8026 Figure 12). line in use before = 5 V are shown © NXP B.V. 2010. All rights reserved ...

Page 38

... IO_SR[0]/IO_SR[2] (low) and IO_SR[1]/IO_SR[3] (high) is LOW (see table page 37). 8.11 Fault detection The following fault conditions are monitored by the TDA8026. • Overheating: All the card slots are automatically deactivated and the device is forced in to Standby mode when the detected temperature range is between 125 C to 209 C ...

Page 39

... PRES, RST pins on all other pins MM on all pins CDM on all pins Thermal characteristics Parameter thermal resistance from junction to ambient All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC Min 0.5 0.5 0.5 0.5 [1] 0.5 [1] 0 [2] ...

Page 40

... DC-to-DC converter on [2] ; DC-to-DC converter off; [3] [3] DD [4] = stopped on pins [5] pins = 5 V; CC( CC(5) pins = 5 V; CC(n) [3] DD 11. current load and DC-to-DC converter and CC Conditions Min Typ Max TDA8026 Min Typ Max Unit 2.7 - 5.5 V 5. 100 150 mV 1.6 - 3.6 V 2.35 2.45 2.55 V 1.19 1.26 1. 300 450 ...

Page 41

... V card; 40 nAs current spikes 3 V card; 17.5 nAs current spikes 1.8 V card; 11.1 nAs current spikes on pins kHz < card CC(n) clock frequency < 200 MHz All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC Min Typ Max 2.1 2.8 3.5 5.25 5 ...

Page 42

... V 0.4 - CC(n) V 0.5 - CC( 0.4 - CC(n) V 0.5 - CC( TDA8026 and Max Unit 0. 240 nF 0 CC( CC(n) 0.4 V 0.1 s 0.1 s 0 CC( CC(n) 0 MHz © ...

Page 43

... V 0.4 - CC(n) 0.9V - CC(n) 0.8V - CC(n) 0.7V - CC( 0.3 - 0.6V - CC(n) 0.7V - CC [3 TDA8026 and Max Unit 55 % V/ns 0 CC( 0.1 V CC( 0.1 V CC( 0.1 V CC(n) 0 CC( CC( 650 400 ns 1.2 s 1.2 s 0 500 kHz © NXP B.V. 2010. All rights reserved. ...

Page 44

... Min Typ Max 0 - 0.3 0 DD(INTF) DD(INTF) 0. DD(INTF) DD(INTF) 0.3 - +0. DD(INTF) DD(INTF 600 - 0.19V - DD(INTF TDA8026 and Unit V DD(INTF) + 0.3 V DD(INTF and Max Unit 135 s 100 and Unit DD(INTF © ...

Page 45

... V 0 DD(INTF) DD(INTF 0.14V - DD(INTF 0.3 - +0 DD(INTF) DD(INTF 2.5 3 TDA8026 and Unit MHz V DD(INTF) V DD(INTF clk(ext) ns clk(ext) V DD(INTF DD(INTF © NXP B.V. 2010. All rights reserved. ...

Page 46

... V 0 DD(INTF) DD(INTF 0 0 DD(INTF) DD(INTF DD(INTF) DD(INTF TDA8026 and Unit V DD(INTF DD(INTF © NXP B.V. 2010. All rights reserved ...

Page 47

... Multiple smart card slot interface IC Min Typ Max 0.3 - +0 DD(INTF) DD(INTF 0 0.3 - +0 DD(INTF) DD(INTF 400 100 - - - - 300 - - 300 0 TDA8026 and Unit V DD(INTF DD(INTF kHz © NXP B.V. 2010. All rights reserved ...

Page 48

... CC(n) active mode; DC-to-DC converter SU;DAT t SU;STA t HIGH Sr 2 C-bus All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC and V DD Min Typ 125 167 80 120 ...

Page 49

... CLKIN1 CLKIN2 SPRES GND2 to GND10 TESTMODE INHIB TST1 TST2 (1) Low ESR capacitor, placed near the IC. (2) Low ESR capacitor, placed near the C1 connector contact. Fig 14. Application diagram: TDA8026 with one card and four SAMs ...

Page 50

... All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 Multiple smart card slot interface detail 0.15 0.08 0.12 0.1 EUROPEAN PROJECTION TDA8026 SOT1073-1 ISSUE DATE 08-03-06 08-03-14 © NXP B.V. 2010. All rights reserved ...

Page 51

... Solder bath specifications, including temperature and impurities TDA8026_1 Product data sheet All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC © NXP B.V. 2010. All rights reserved ...

Page 52

... Package reflow temperature ( C) 3 Volume (mm ) < 350 260 260 250 Figure 16. All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC Figure 16) than a SnPb process, thus 350 220 220 350 to 2000 > 2000 260 260 250 ...

Page 53

... Most Significant Bit Printed-Circuit Board Power-On Reset Point Of Sales Security Access Module Data sheet status Product data sheet All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC peak temperature 001aac844 Change notice Supersedes - 1.2 © ...

Page 54

... NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC © NXP B.V. 2010. All rights reserved ...

Page 55

... I C-bus — logo is a trademark of NXP B.V. http://www.nxp.com salesaddresses@nxp.com All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC © NXP B.V. 2010. All rights reserved ...

Page 56

... NXP Semiconductors 19. Tables Table 1. Quick reference data . . . . . . . . . . . . . . . . . . . . .2 Table 2. Ordering information . . . . . . . . . . . . . . . . . . . . .3 Table 3. TDA8026 ball map . . . . . . . . . . . . . . . . . . . . . . .5 Table 4. Pin description . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 5. Base addressing . . . . . . . . . . . . . . . . . . . . . . .14 Table 6. Write mode addresses . . . . . . . . . . . . . . . . . .14 Table 7. Register overview . . . . . . . . . . . . . . . . . . . . . .16 Table 8. Bank 0 register (address: 48h) bit allocation . .18 Table 9. Bank 0 bit description . . . . . . . . . . . . . . . . . . .18 Table 10. Bank 1 CSb[7:0] Register0 (address 40h) card slot 1 and card slot 2 bit allocation ...

Page 57

... NXP Semiconductors 20. Figures Fig 1. TDA8026 Block diagram . . . . . . . . . . . . . . . . . . . .4 Fig 2. TDA8026 pin configuration for the TFBGA64 package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Fig 3. TDA8026 Power diagram . . . . . . . . . . . . . . . . . . . .8 Fig 4. The enter shutdown sequence .10 Fig 5. The exit shutdown sequence . . . . . . . . . . . . . . . .10 Fig 6. The voltage supervisor circuit . . . . . . . . . . . . . . .11 Fig 7. V voltage supervisor . . . . . . . . . . . . . . . . . . . .11 DD Fig 8. ...

Page 58

... Bank 1 Register1 (REG[1:0] = 10) card slot 3 (address 03h), card slot 4 (address 04h) and card slot 5 (address 05h) bit allocation . . . . . . . . . 28 All information provided in this document is subject to legal disclaimers. Rev. 1 — 9 March 2010 TDA8026 Multiple smart card slot interface IC continued >> © NXP B.V. 2010. All rights reserved ...

Page 59

... Please be aware that important notices concerning this document and the product(s) described herein, have been included in section ‘Legal information’. © NXP B.V. 2010. For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com TDA8026 All rights reserved. Date of release: 9 March 2010 Document identifier: TDA8026_1 ...