UPD78F0386GK-8EU-A Renesas Electronics America, UPD78F0386GK-8EU-A Datasheet - Page 366

UPD78F0386GK-8EU-A

Manufacturer Part Number

UPD78F0386GK-8EU-A

Description

MCU 96KB FLASH 5KB RAM

Manufacturer

Renesas Electronics America

Series

78K0/Lx2r

Datasheet

1.UPD78F0372GK-8EU-A.pdf

(624 pages)

Specifications of UPD78F0386GK-8EU-A

Core Processor

78K/0

Core Size

8-Bit

Speed

20MHz

Connectivity

3-Wire SIO, I²C, LIN, UART/USART

Peripherals

LCD, LVD, POR, PWM, WDT

Number Of I /o

26

Program Memory Size

96KB (96K x 8)

Program Memory Type

FLASH

Ram Size

5K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

- Current page: 366 of 624

- Download datasheet (5Mb)

364

(4) IIC clock selection register 0 (IICCL0)

Address: FFA8H

Condition for clearing (CLD0 = 0)

Condition for clearing (DAD0 = 0)

Digital filter can be used only in high-speed mode.

In high-speed mode, the transfer clock does not vary regardless of DFC0 bit set (1)/clear (0).

The digital filter is used for noise elimination in high-speed mode.

Symbol

IICCL0

This register is used to set the transfer clock for the I

IICCL0 is set by a 1-bit or 8-bit memory manipulation instruction. However, the CLD0 and DAD0 bits are read-

only. The SMC0, CL01, and CL00 bits are set in combination with bit 0 (CLX0) of IIC function expansion

register 0 (IICX0) (see 16.3 (6) I

Set IICCL0 while bit 7 (IICE0) of IIC control register 0 (IICC0) is 0.

Reset signal generation sets IICCL0 to 00H.

Note Bits 4 and 5 are read-only.

Remark

SMC0

When the SCL0 pin is at low level

When IICE0 = 0 (operation stop)

Reset

DAD0

When the SDA0 pin is at low level

When IICE0 = 0 (operation stop)

Reset

DFC0

CLD0

0

1

0

1

0

1

0

1

The SCL0 pin was detected at low level.

The SCL0 pin was detected at high level.

The SDA0 pin was detected at low level.

The SDA0 pin was detected at high level.

Operates in standard mode.

Operates in high-speed mode.

Digital filter off.

Digital filter on.

IICE0: Bit 7 of IIC control register 0 (IICC0)

7

0

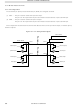

Figure 16-8. Format of IIC Clock Selection Register 0 (IICCL0) (1/2)

Figure 16-8. Format of IIC Clock Selection Register 0 (IICCL0) (2/2)

After reset: 00H

6

0

CHAPTER 16 SERIAL INTERFACE IIC0

2

C transfer clock setting method).

Detection of SDA0 pin level (valid only when IICE0 = 1)

Detection of SCL0 pin level (valid only when IICE0 = 1)

CLD0

<5>

R/W

User’s Manual U17504EJ2V0UD

Note

DAD0

Digital filter operation control

<4>

Operation mode switching

2

C bus.

Condition for setting (CLD0 = 1)

Condition for setting (DAD0 = 1)

When the SCL0 pin is at high level

When the SDA0 pin is at high level

SMC0

<3>

DFC0

<2>

CL01

1

CL00

0

Related parts for UPD78F0386GK-8EU-A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: