A43L2616V-7 AMIC Technology Corporation, A43L2616V-7 Datasheet

A43L2616V-7

Available stocks

Related parts for A43L2616V-7

A43L2616V-7 Summary of contents

Page 1

Document Title Bit X 4 Banks Synchronous DRAM Revision History Rev. No. History 0.0 Initial issue 1.0 Add -V grade 2.0 Add -5.5 spec 3.0 Add Full Page Mode 3.1 Add Pb-Free package type 3.2 art numbering ...

Page 2

... Range of operating frequencies, programmable latencies allows the same device to be useful for a variety of high bandwidth, high performance memory system applications A43L2616V ...

Page 3

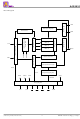

Block Diagram Bank Select CLK ADD LRAS LRAS LCBR CLK (February, 2008, Version 3.2) Data Input Register Column Decoder Latency & Burst Length Programming Register LCAS LWE Timing ...

Page 4

Pin Descriptions Symbol Name CLK System Clock Chip Select CS CKE Clock Enable A0~A11 Address BS0, BS1 Bank Select Address Row Address Strobe RAS Column Address CAS Strobe Write Enable WE Data Input/Output L(U)DQM Mask DQ Data Input/Output 0-15 Power ...

Page 5

Absolute Maximum Ratings* Voltage on any pin relative to VSS (Vin, Vout ) . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

... Note: 1. Measured with outputs open. Addresses are changed only one time during t 2. Refresh period is 64ms. Addresses are changed only one time during normal version: A43L2616V-6, A43L2616V-7. CC6 4. I low self refresh current version: A43L2616V-5.5V, A43L2616V-6V, A43L2616V-7V. CC6 (February, 2008, Version 3.2) Symbol C DC1 ...

Page 7

AC Operating Test Conditions (VDD = 3.3V ± 0.3V ° +70 ° Parameter AC input levels Input timing measurement reference level Input rise and all time (See note3) Output timing measurement reference level ...

Page 8

Operating AC Parameter (AC operating conditions unless otherwise noted) Symbol Parameter t Row active to row active delay RRD(min) t RCD(min) RAS to CAS delay t Row precharge time RP(min) t RAS(min) Row active time t RAS(max) t Row cycle ...

Page 9

Simplified Truth Table Command Register Mode Register Set Refresh Auto Refresh Entry Self Refresh Exit Bank Active & Row Addr. Read & Auto Precharge Disable Column Addr. Auto Precharge Enable Write & Auto Precharge Disable Column Addr. Auto Precharge Enable ...

Page 10

Mode Register Filed Table to Program Modes Register Programmed with MRS Address BS0, BS1 A11, A10 Function RFU RFU (Note 1) (Note 2) Test Mode A8 A7 Type 0 0 Mode Register Set 0 1 Vendor Use 1 0 Only ...

Page 11

Burst Sequence (Burst Length = 4) Initial address Burst Sequence (Burst Length = 8) Initial address ...

Page 12

Device Operations Clock (CLK) The clock input is used as the reference for all SDRAM operations. All operations are synchronized to the positive going edge of the clock. The clock transitions must be monotonic between VIL and VIH. During operation ...

Page 13

Device Operations (continued) Bank Activate The bank activate command is used to select a random row in an idle bank. By asserting low on RAS and CS with desired row and bank addresses, a row access is initiated. The read ...

Page 14

Device Operations (continued) Auto Precharge The precharge operation can also be performed by using auto precharge. The SDRAM internally generates the timing to satisfy t (min) and “t RAS RP burst length and CAS latency. The auto precharge command is ...

Page 15

Basic feature And Function Descriptions 1. CLOCK Suspend 1) Click Suspended During Write (BL=4) CLK CMD WR CKE Masked by CKE Internal CLK DQ(CL2 DQ(CL3 Not Written Note: CLK to CLK disable/enable=1 clock 2. DQM Operation ...

Page 16

CAS Interrupt (I) 1) Read interrupted by Read (BL=4) CLK CMD RD RD ADD A B DQ(CL2) QA0 DQ(CL3) t CCD Note2 2) Write interrupted by Write (BL =2) CLK WR WR CMD t CCD Note2 ADD A B ...

Page 17

CAS Interrupt (II) : Read Interrupted Write & DQM (1) CL=2, BL=4 CLK i) CMD RD DQM DQ ii) CMD RD DQM DQ RD iii) CMD DQM DQ iv) CMD RD DQM DQ (2) CL=3, BL=4 CLK i) CMD ...

Page 18

Write Interrupted by Precharge & DQM CLK CMD WR DQM Masked by DQM Note : 1. To inhibit invalid write, DQM should be issued. 2. This precharge command and burst write command should be of ...

Page 19

Burst Stop & Interrupted by Precharge 1) Normal Write (BL=4) CLK CMD WR DQM Read Interrupted by Precharge (BL=4) CLK CMD RD PRE DQ(CL2) Q0 DQ(CL3) 9. MRS Mode Register Set CLK Note 1 ...

Page 20

Auto Refresh & Self Refresh Note 3 1) Auto Refresh CLK Note 4 CKE PRE Internal CLK CMD Note 6 2) Self Refresh CLK Note 4 CMD PRE CKE * Note : 1. Active power down : one or ...

Page 21

About Burst Type Control Sequential counting Basic MODE Interleave counting Random Random column Access MODE CLK CCD 13. About Burst Length Control 1 Basic 2 MODE 4 8 Special BRSW MODE RAS Interrupt (Interrupted by Precharge) ...

Page 22

Power On Sequence & Auto Refresh CLOCK CKE High level is necessary RAS CAS ADDR BS0, BS1 A10/AP WE DQM High level is necessary High-Z DQ Precharge Auto Refresh (All Banks) (February, ...

Page 23

Single Bit Read-Write-Read Cycles (Same Page) @CAS Latency=3, Burst Length CLOCK CKE *Note RCD t SH RAS CAS ...

Page 24

Note : 1. All inputs can be don’t care when CS is high at the CLK high going edge. 2. Bank active & read/write are controlled by BS0, BS1. BS1 Enable and disable auto ...

Page 25

Read & Write Cycle at Same Bank @Burst Length CLOCK CKE CS t RCD RAS CAS ADDR Ra Ca0 BS0 BS1 A10/ DQM DQ ( RAC t *Note 3 SAC ...

Page 26

Page Read & Write Cycle at Same Bank @Burst Length CLOCK CKE CS t RCD RAS CAS ADDR Ra Ca BS0 BS1 A10/ DQM DQ (CL=2) DQ (CL=3) Row Active Read (A-Bank) (A-Bank) ...

Page 27

Page Read Cycle at Different Bank @Burst Length = CLOCK CKE *Note 1 CS RAS CAS RAa RBb CAa ADDR BS1 BS0 A10/AP RAa RBb WE DQM DQ (CL=2) DQ (CL=3) Read Row Active ...

Page 28

Page Write Cycle at Different Bank @Burst Length CLOCK CKE CS RAS CAS RAa RBb CAa ADDR BS1 BS0 A10/AP RAa RBb DAa0 DAa1 DQ WE DQM Write Row Active (A-Bank) (A-Bank) Row Active (B-Bank) ...

Page 29

Read & Write Cycle at Different Bank @Burst Length CLOCK CKE CS RAS CAS RAa CAa ADDR BS1 BS0 A10/AP RAa WE DQM DQ (CL=2) DQ (CL=3) Row Active Read (A-Bank) (A-Bank) * Note : ...

Page 30

Read & Write Cycle with Auto Precharge @Burst Length CLOCK CKE CS RAS CAS RAa RBb ADDR BS1 BS0 RAa RBb A10/AP WE DQM DQ (CL=2) DQ (CL=3) Row Active (A-Bank) Auto Precharge Row Active ...

Page 31

Clock Suspension & DQM Operation Cycle @CAS Latency = 2, Burst Length CLOCK CKE CS RAS CAS Ra Ca ADDR BS1 BS0 A10/ DQM DQ Row Active Read Suspension * Note : DQM ...

Page 32

Read Interrupted by Precharge Command & Read Burst Stop Cycle @Burst Length=Full Page CLOCK CKE CS RAS CAS RAa CAa ADDR BS1 BS0 RAa A10/AP WE DQM DQ (CL=2) DQ (CL=3) Read Row Active (A-Bank) ...

Page 33

Write Interrupted by Precharge Command & Write Burst Stop Cycle @ Burst Length = Full Page CLOCK CKE CS RAS CAS RAa CAa ADDR BS1 BS0 A10/AP RAa WE DQM DAa0 DQ Write Row Active ...

Page 34

Active/Precharge Power Down Mode @CAS Lantency=2, Burst Length CLOCK t SS CKE * Note 1 *Note 3 CS RAS CAS ADDR BS1 BS0 A10/AP WE DQM DQ Precharge Power-down Entry * Note : 1. All ...

Page 35

Self Refresh Entry & Exit Cycle CLOCK * Note 2 CKE * Note RAS * Note 7 CAS ADDR BS0, BS1 A10/AP WE DQM DQ Hi-Z Self Refresh Entry * Note ...

Page 36

Mode Register Set Cycle CLOCK CKE High *Note 2 CS RAS * Note 1 CAS * Note 3 Key Ra ADDR WE DQM DQ Hi-Z MRS New Command * Both banks precharge should be completed ...

Page 37

Function Truth Table (Table 1) Current CS RAS CAS State IDLE ...

Page 38

Function Truth Table (Table 1, Continued) Current CS RAS CAS State Write with Auto Precharge ...

Page 39

Function Truth Table for CKE (Table 2) Current CKE CKE CS State n Self Refresh ...

Page 40

Numbering Scheme P A43 Optional (February, 2008, Version 3. A43L2616 X Package Material Blank: normal F: PB free Temperature ° ° Blank : ° ...

Page 41

... Ordering Information Part No. Cycle Time (ns) A43L2616V-6 A43L2616V-6F A43L2616V-7 A43L2616V-7F A43L2616V-5.5V A43L2616V-5.5VF A43L2616V-6V A43L2616V-6VF A43L2616V-7V A43L2616V-7VF Low Self Refresh Current version for –V grade 183Mhz is only available for -V grade (A43L2616V-5.5V). (February, 2008, Version 3.2) Clock Frequency (MHz) 6 166 @ 143 @ 5.5 183 @ ...

Page 42

Package Information TSOP 54 (Type II) Outline Dimensions - Seating Plane Symbol Notes: 1. The maximum value of dimension D includes end flash. 2. Dimension E does not include resin fins. 3. Dimension S ...