LMH0031VS/NOPB National Semiconductor, LMH0031VS/NOPB Datasheet - Page 12

LMH0031VS/NOPB

Manufacturer Part Number

LMH0031VS/NOPB

Description

IC DESER/DESCRAM DGTL VID 64TQFP

Manufacturer

National Semiconductor

Type

Descrambler/Deserializerr

Datasheet

1.LMH0031VSNOPB.pdf

(31 pages)

Specifications of LMH0031VS/NOPB

Applications

SDTV/HDTV

Mounting Type

Surface Mount

Package / Case

64-TQFP, 64-VQFP

Input Voltage

3.3 V

Supply Voltage (max)

3.45 V

Supply Voltage (min)

3.15 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

For Use With

SD131EVK - BOARD EVALUATION LMH0031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LMH0031VS/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

www.national.com

Device Operation

ANCILLARY/CONTROL DATA PATH

The 10-bit ancillary and Control Data Port AD[9:0] serves

two functions in the LMH0031. Ancillary Data from the An-

cillary Data FIFO is output from this port after its recovery

from the video data stream. The utilization and flow of Ancil-

lary Data from the device is managed by a system of control

bits, masks and IDs stored in the control data registers. This

port also provides read/write access to contents of the con-

figuration and control registers. The signals RD/WR, ANC/

CTRL and A

CONTROL DATA FUNCTIONS

Control data is input to and output from the LMH0031 using

the lower-order 8 bits AD[7:0] of the ancillary/Control Data

Port. This control data initializes, monitors and controls op-

eration of the LMH0031. The upper two bits AD[9:8] of the

port function as handshaking signals with the device access-

ing the port. When either a control register read or write

address is being written to the port, AD[9:8] must be driven

as 00b (0XXh, where XX are AD[7:0]). When control data is

being written to the port, AD[9:8] must be driven as 11b

(3XXh, where XX are AD[7:0]). When control data is being

read from the port, the LMH0031 will output AD[9:8] as 10b

(2XXh, where XX are output data AD[7:0]) and may be

ignored by the monitoring system.

Note: After either a manual or power-on reset, A

toggled three (3) times to complete initiallization of the An-

cillary and Control Data Port.

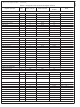

The sequence of clock and control signals for reading control

data from the ancillary/control data port is shown in Figure 2.

Control data read mode is invoked by making the ANC/

CTRL input low and the RD/WR input high. The 8-bit ad-

dress of the control register set to be accessed is input to the

port on bits AD[7:0]. To identify the data as an address,

AD[9:8] must be driven as 00b. The complete address word

will be 0XXh, where 0 is AD[9:8] and XX are AD[7:0]. The

address is captured on the rising edge of A

control data is being read from the port, the LMH0031 will

output AD[9:8] as 10b (2XXh, where XX are output data

AD[7:0]) and may be ignored by the monitoring system. Data

being output from the selected register is driven by the port

immediately following the rising edge of A

address signal is removed. For optimum system timing, the

signals driving the address to the port should be removed

CLK

control data flow through the port.

(Continued)

CLK

or when the

CLK

CLK

must be

. When

12

immediately after the address is clocked into the port and

before or simultaneously with the falling edge of A

end of that address cycle. Output data remains stable until

the next rising edge of A

devices at any time after the removal of the address signal.

This second clock resets the port from drive to receive and

readies the port for another access cycle.

Example: Read the Full-field Flags via the AD port.

1. Set ANC/CTRL to a logic-low.

2. Set RD/WR to a logic-high.

3. Present 001h to AD[9:0] as the register address.

4. Toggle A

5. Release the bus driving the AD port.

6. Read the data present on the AD port. The Full-field

7. Toggle A

Figure 3 shows the sequence of clock and control signals for

writing control data to the ancillary/control data port. The

control data write mode is similar to the read mode. Con-

trol data write mode is invoked by making the ANC/CTRL

input low and the RD/WR input low. The 8-bit address of the

control register set to be accessed is input to the port on bits

AD[7:0]. When a control register write address is being

written to the port, AD[9:8] must be driven as 00b (0XXh,

where XX are AD[7:0]). The address is captured on the rising

edge of A

edge of A

bits AD[7:0] and written into the selected register on the next

rising edge of A

port, AD[9:8] must be driven as 11b (3XXh, where XX are

AD[7:0]). Control data written into the registers may be read

out non-destructively in most cases.

Example: Setup (without enabling) the TPG Mode via the

AD port using the 1125 line, 30 frame, 74.25MHz, interlaced

component (SMPTE 274M) colour bars as test pattern. The

TPG may be enabled after setup using the Multi-function I/O

port or by the control registers.

1. Set ANC/CTRL to a logic-low.

2. Set RD/WR to a logic-low.

3. Present 00Dh to AD[9:0] as the Test 0 register address.

4. Toggle A

5. Present 327h to AD[9:0] as the register data.

6. Toggle A

Flags are bits AD[4:0].

CLK

CLK

CLK

CLK

CLK

CLK

. Next, the control data is presented to the port

. The address data is removed on the falling

CLK

.

.

.

to release the AD port.

. When control data is being written to the

CLK

and may be written into external

CLK

at the