k4d263238m-qc60 Samsung Semiconductor, Inc., k4d263238m-qc60 Datasheet - Page 8

k4d263238m-qc60

Manufacturer Part Number

k4d263238m-qc60

Description

1m X 32bit X 4 Banks Double Data Rate Synchronous Ram With Bi-directional Data Strobe And Dll

Manufacturer

Samsung Semiconductor, Inc.

Datasheet

1.K4D263238M-QC60.pdf

(19 pages)

K4D263238M

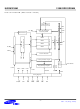

FUNCTIONAL DESCRIPTION

• Power-Up Sequence

DDR SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations.

Command

*1

*

Power up & Initialization Sequence

1,2

stable for 200us

7. Issue precharge command for all banks of the device.

4. Issue precharge command for all banks of the device.

6. Issue a MRS command to reset DLL. The additional 200 clock cycles are required to lock the DLL.

1. Apply power and keep CKE at low state (All other inputs may be undefined)

2. Start clock and maintain stable condition for minimum 200us.

3. The minimum of 200us after stable power and clock(CK,CK ), apply NOP and take CKE to be high.

5. Issue a EMRS command to enable DLL

8. Issue at least 2 or more auto-refresh commands.

9. Issue a mode register set command with A8 to low to initialize the mode register.

Inputs must be

*1 The additional 200cycles of clock input is required to lock the DLL after enabling DLL.

*2 Sequence of 6&7 is regardless of the order.

CK

CK

- Apply VDD before VDDQ .

- Apply VDDQ before VREF & VTT

0

ALL Banks

precharge

1

2

t

RP

3

EMRS

4

2 Clock min.

5

DLL Reset

MRS

6

2 Clock min.

7

ALL Banks

precharge

8

- 8 -

9

tRP

10

1st Auto

Refresh

200 Clock min.

11

t

12

RFC

13

2nd Auto

Refresh

14

128M DDR SDRAM

15

t

RFC

Rev. 1.3 (Aug. 2001)

16

17

Register Set

Mode

18

2 Clock min.

19

Command

Any