LTC3719EG Linear Technology, LTC3719EG Datasheet - Page 8

LTC3719EG

Manufacturer Part Number

LTC3719EG

Description

IC SW REG SYNC STEP-DOWN 36-SSOP

Manufacturer

Linear Technology

Datasheet

1.LTC3719EG.pdf

(32 pages)

Specifications of LTC3719EG

Applications

Controller, AMD Opteron™

Voltage - Input

4 ~ 36 V

Number Of Outputs

1

Voltage - Output

0.8 ~ 1.55 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

36-SSOP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LTC3719EG

Manufacturer:

LINEAR/凌特

Quantity:

20 000

Part Number:

LTC3719EG#PBF

Manufacturer:

LT/凌特

Quantity:

20 000

Company:

Part Number:

LTC3719EG#TR

Manufacturer:

LT

Quantity:

2 300

Part Number:

LTC3719EG#TRPBF

Manufacturer:

LINEAR/凌特

Quantity:

20 000

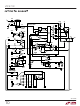

LTC3719

PI FU CTIO S

RUN/SS (Pin 1): Combination of Soft-Start, Run Control

Input and Short-Circuit Detection Timer. A capacitor to

ground at this pin sets the ramp time to full current output.

Forcing this pin below 0.8V causes the IC to shut down all

internal circuitry. All functions are disabled in shutdown.

SENSE1

Differential Current Comparator. The I

built-in offsets between SENSE

conjunction with R

SENSE1

Differential Current Comparators.

EAIN (Pin 4): Input to the error amplifier that compares the

feedback voltage to the internal 0.6V reference voltage.

This pin is normally connected to a resistive divider from

the output of the differential amplifier (DIFFOUT).

PLLFLTR (Pin 5): The phase-locked loop’s lowpass filter

is tied to this pin. Alternatively, this pin can be driven with

an AC or DC voltage source to vary the frequency of the

internal oscillator. Do not apply voltage to this pin prior to

application of V

PLLIN (Pin 6): External Synchronization Input to Phase

Detector. This pin is internally terminated to SGND with

50k . The phase-locked loop will force the rising top gate

signal of controller 1 to be synchronized with the rising

edge of the PLLIN signal.

FCB (Pin 7): Forced Continuous Control Input. This input

acts on both output stages. Pulling this pin below 0.6V

will force continuous synchronous operation. Do not

leave this pin floating without a decoupling capacitor.

8

U

+

–

, SENSE2

, SENSE2

U

IN

.

SENSE

+

–

U

(Pins 2,14): The (+) Input to Each

(Pins 3,13): The (–) Input to the

set the current trip threshold.

–

and SENSE

TH

pin voltage and

+

pins in

I

tor Compensation Point. Both current comparator’s thresh-

olds increase with this control voltage. The normal voltage

range of this pin is from 0V to 2.4V

SGND (Pin 9): Signal Ground. This pin is common to both

controllers. Route separately to the PGND pin.

V

pin provides true remote output voltage sensing. V

normally drives an external resistive divider that sets the

output voltage.

V

fier. Internal precision resistors configure it as a differen-

tial amplifier whose output is V

ATTENOUT (Pin 15): Voltage Feedback Signal Resistively

Divided According to the VID Programming Code.

NO_CPU (Pin 16): Open-Drain Logic Output. NO_CPU is

pulled to ground if VID0 to VID3 are all high.

VID0–VID4 (Pins 17,18, 19, 20, 21): VID Control Logic

Input Pins.

V

ATTENIN (Pin 23): The Input to the VID Controlled Resis-

tive Divider.

TG2, TG1 (Pins 24, 35): High Current Gate Drives for Top

N-Channel MOSFETS. These are the outputs of floating

drivers with a voltage swing equal to INTV

posed on the switch node voltage SW.

TH

DIFFOUT

OS

BIAS

(Pin 8): Error Amplifier Output and Switching Regula-

–

, V

(Pin 22): Supply Pin for the VID Control Circuit.

OS

(Pin 10): Output of a Differential Amplifier. This

+

(Pins 11, 12): Inputs to an Operational Ampli-

DIFFOUT

.

CC

superim-

sn3719 3719fs

DIFFOUT