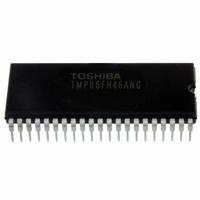

TMP86FH46ANG(Z) Toshiba, TMP86FH46ANG(Z) Datasheet - Page 27

TMP86FH46ANG(Z)

Manufacturer Part Number

TMP86FH46ANG(Z)

Description

IC MCU 8BIT FLASH 16KB 42-SDIP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FH46ANGZ.pdf

(214 pages)

Specifications of TMP86FH46ANG(Z)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

33

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

42-SDIP (0.600", 15.24mm)

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

33

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

BMSKTOPAS86FH47(AND), BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP86C909XB - EMULATION CHIP FOR TMP86F SDIP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FH46ANGZ

- Current page: 27 of 214

- Download datasheet (3Mb)

2.2.3.3

internal status immediately prior to the halt is held with a lowest power consumption during STOP mode.

inputting (Either level-sensitive or edge-sensitive can be programmably selected) to the

the warm-up period is completed, the execution resumes with the instruction which follows the STOP

mode start instruction.

(4)

(5)

(6)

(7)

STOP mode

In this mode, the internal oscillation circuit is turned off, causing all system operations to be halted. The

STOP mode is started by the system control register 1 (SYSCR1), and STOP mode is released by a

SYSCR2<XEN>. In SLOW1 and SLEEP modes, the input clock to the 1st stage of the divider is

stopped; output from the 1st to 6th stages is also stopped.

halted; however, on-chip peripherals remain active (Operate using the high-frequency clock and/or

the low-frequency clock). Starting and releasing of IDLE2 mode are the same as for IDLE1 mode,

except that operation returns to NORMAL2 mode.

the watchdog timer, and the internal oscillation circuit of the high-frequency clock are halted; how-

ever, on-chip peripherals remain active (Operate using the low-frequency clock). Starting and releas-

ing of SLEEP mode are the same as for IDLE1 mode, except that operation returns to SLOW1 mode.

In SLOW1 and SLEEP1 modes, the input clock to the 1st stage of the divider is stopped; output from

the 1st to 6th stages is also stopped.

SLEEP2 mode is same as that under the SLEEP1 mode, except for the oscillation circuit of the high-

frequency clock.

is enabled by setting “1” on bit SYSCR2<TGHALT>.

peripheral circuits other than TBT. Then, upon detecting the falling edge of the source clock selected

with TBTCR<TBTCK>, the timing generator starts feeding the clock to all peripheral circuits.

again. SLEEP0 mode is entered and returned regardless of how TBTCR<TBTEN> is set. When IMF

= “1”, EF6 (TBT interrupt individual enable flag) = “1”, and TBTCR<TBTEN> = “1”, interrupt pro-

cessing is performed. When SLEEP0 mode is entered while TBTCR<TBTEN> = “1”, the INTTBT

interrupt latch is set after returning to SLOW1 mode.

Switching back and forth between SLOW1 and SLOW2 modes are performed by

IDLE2 mode

In this mode, the internal oscillation circuit remain active. The CPU and the watchdog timer are

SLEEP1 mode

In this mode, the internal oscillation circuit of the low-frequency clock remains active. The CPU,

SLEEP2 mode

The SLEEP2 mode is the idle mode corresponding to the SLOW2 mode. The status under the

SLEEP0 mode

In this mode, all the circuit, except oscillator and the timer-base-timer, stops operation. This mode

When SLEEP0 mode starts, the CPU stops and the timing generator stops feeding the clock to the

When returned from SLEEP0 mode, the CPU restarts operating, entering SLOW1 mode back

Page 13

TMP86FH46ANG

STOP

pin. After

Related parts for TMP86FH46ANG(Z)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: