PIC17C756-16/L Microchip Technology, PIC17C756-16/L Datasheet

PIC17C756-16/L

Specifications of PIC17C756-16/L

Related parts for PIC17C756-16/L

PIC17C756-16/L Summary of contents

Page 1

... High-Performance 8-Bit CMOS EPROM Microcontrollers Devices included in this data sheet: • PIC17C752 • PIC17C756 Microcontroller Core Features: • Only 58 single word instructions to learn • All single cycle instructions (121 ns) except for program branches and table reads/writes which are two-cycle • Operating speed: ...

Page 2

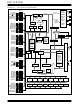

... PIC17C75X IN 68-PIN LCC 10 RD1/AD9 11 RD0/AD8 12 RE0/ALE 13 RE1/OE 14 RE2/WR 15 RE3/CAP4 16 MCLR TEST RF7/AN11 22 RF6/AN10 23 RF5/AN9 RF4/AN8 24 RF3/AN7 25 26 RF2/AN6 DS30264A-page 2 60 RA0/INT 59 RB0/CAP1 58 RB1/CAP2 57 RB3/PWM2 56 RB4/TCLK12 55 RB5/TCLK3 54 RB2/PWM1 PIC17C75X Top View 51 OSC2/CLKOUT 50 OSC1/CLKIN RB7/SDO 47 RB6/SCK 46 RA3/SDI/SDA 45 RA2/SS/SCL 44 RA1/T0CKI Preliminary 1997 Microchip Technology Inc. ...

Page 3

... RD3/AD11 RD2/AD10 RD1/AD9 RD0/AD8 RE0/ALE RE1/OE RE2/WR RE3/CAP4 MCLR/V PP TEST RF7/AN11 RF6/AN10 RF5/AN9 RF4/AN8 RF3/AN7 RF2/AN6 RF1/AN5 RF0/AN4 RG3/AN0/V + REF RG2/AN1/V - REF RG1/AN2 RG0/AN3 1997 Microchip Technology Inc PIC17C75X 41 Top View Applicable TQFP RC1/AD1 2 63 RC2/AD2 3 62 RC3/AD3 4 61 RC4/AD4 5 60 ...

Page 4

... If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a bet- ter document. DS30264A-page 4 To Our Valued Customers Preliminary 1997 Microchip Technology Inc. ...

Page 5

... OVERVIEW This data sheet covers the PIC17C75X group of the PIC17CXXX family of microcontrollers. The following devices are discussed in this data sheet: • PIC17C752 • PIC17C756 The PIC17C75X devices are 68-Pin, EPROM-based members of the versatile PIC17CXXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers. ...

Page 6

... DIP 40-pin DIP 40-pin DIP 44-pin PLCC 44-pin PLCC 44-pin PLCC 44-pin MQFP 44-pin MQFP 44-pin MQFP 44-pin TQFP 44-pin TQFP 44-pin TQFP Preliminary PIC17C44 PIC17C752 PIC17C756 33 MHz 33 MHz 33 MHz 2.5 - 6.0V 3.0 - 6.0V 3 16K - - - 454 454 902 ...

Page 7

... EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before produc- tion shipments are available. Please contact your local Microchip Technology sales office for more details. 2.4 Serialized Quick-Turnaround Production (SQTP Microchip offers a unique programming service where a few user-defi ...

Page 8

... Being electrically erasable, these devices can be erased and reprogrammed in-circuit. These devices are the same for prototype development, pilot programs, as well as production. Note: Presently, NO Flash versions of the PIC17C75X devices are available. DS30264A-page 8 Preliminary 1997 Microchip Technology Inc. ...

Page 9

... The PIC17CXXX can address up to 64K pro- gram memory space. The PIC17C752 integrates EPROM pro- gram memory on-chip. The PIC17C756 integrates 16K x 16 EPROM program memory. Program execution can be internal only (microcontrol- ler or protected microcontroller mode), external only (microprocessor mode) or both (extended microcon- troller mode) ...

Page 10

... Signals Test Mode Select Test IR Latch <16> Decode F9 ROM Latch <16> 8 AD<15:0> PORTC, PORTD Data Latch Program Memory (EPROM) 17C756 16K x 16 17C752 ALE, Address WR, Latch OE, PORTE 16 16 10-bit Capture2 SSP A/D IR<7> Interrupt Capture3 Capture4 Module 1997 Microchip Technology Inc. ...

Page 11

... RB7/SDO Legend Input only Output only; I/O = Input/Output Power; — = Not Used; TTL = TTL input Schmitt Trigger input. † The output is only available by the Peripheral operation. 1997 Microchip Technology Inc. I/O/P Buffer Description Type Type I ST Oscillator input in crystal/resonator or RC oscillator mode. ...

Page 12

... I/O ST RF2 can also be analog input 6. I/O ST RF3 can also be analog input 7. I/O ST RF4 can also be analog input 8. I/O ST RF5 can also be analog input 9. I/O ST RF6 can also be analog input 10. I/O ST RF7 can slso be analog input 11. Preliminary 1997 Microchip Technology Inc. ...

Page 13

... Legend Input only Output only; I/O = Input/Output Power; — = Not Used; TTL = TTL input Schmitt Trigger input. † The output is only available by the Peripheral operation. 1997 Microchip Technology Inc. I/O/P Buffer Description Type Type PORTG is a bi-directional I/O Port. ...

Page 14

... NOTES: DS30264A-page 14 Preliminary 1997 Microchip Technology Inc. ...

Page 15

... The main difference between the LF and XT modes is the gain of the internal inverter of the oscillator circuit which allows the different frequency ranges. For more details on the device configuration bits, see Section 17.0. 1997 Microchip Technology Inc. 4.1.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS modes, a crystal or ceramic resonator is ...

Page 16

... OSC2 PIC17CXXX 2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (3) ( (1) 100-150 pF 100-150 pF 10-33 pF 10-33 pF 10-33 pF 10-33 pF 47-100 pF 47-100 pF 15-68 pF 15-68 pF (2) 15-47 pF 15-47 pF TBD TBD 15-47 pF 15- may be S > 4.5V recom- 20 PPM 50 PPM 50 PPM 50 PPM 50 PPM TBD 50 PPM 50 PPM 1997 Microchip Technology Inc. ...

Page 17

... OSC1 Clock from PIC17CXXX ext. system CLKOUT OSC2 (F /4) OSC 1997 Microchip Technology Inc. 4.1.4 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT mode, the Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepack- ). aged oscillators provide a wide operating range and better stability ...

Page 18

... D032 and D042 in the electrical specification section). The time required for the RC to start oscillat- ing depends on many factors. These include: • Resistor value used • Capacitor value used • Device V rise time DD • System temperature Internal clock Preliminary 1997 Microchip Technology Inc. ...

Page 19

... Instruction @ address SUB_1 All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is “flushed” from the pipeline while the new instruction is being fetched and then executed. 1997 Microchip Technology Inc. 4.3 Instruction Flow/Pipelining An “ ...

Page 20

... NOTES: DS30264A-page 20 Preliminary 1997 Microchip Technology Inc. ...

Page 21

... On-chip 10-bit Ripple counter RC OSC† † This RC oscillator is shared with the WDT when not in a power-up sequence. 1997 Microchip Technology Inc. Note: While the device reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external ...

Page 22

... Tosc1 = time for the crystal oscillator to react to an oscil- pin PP lation level detectable by the Oscillator Start-up Timer (ost 1024T OST Preliminary to rise to an acceptable level delay after MCLR is OSC OSCILLATOR START-UP TIME POR or BOR Trip Point OSC T OST T PWRT . OSC 1997 Microchip Technology Inc. ...

Page 23

... The Program Counter = 0, that is, the device branches to the reset vector. This is different from the mid-range devices. 4: When BOR is enabled, else the BOR status bit is unknown. 1997 Microchip Technology Inc. If the device voltage is not within electrical specification at the end of a time-out, the MCLR/V held low until the voltage is within the device specifi ...

Page 24

... INTERNAL POR PWRT TIME-OUT OST TIME-OUT INTERNAL RESET FIGURE 5-7: SLOW RISE TIME (MCLR TIED MCLR INTERNAL POR PWRT TIME-OUT OST TIME-OUT INTERNAL RESET DS30264A-page 24 > PWRT OST T PWRT T OST T PWRT T OST ) DD Minimum V operating voltage PWRT T OST Preliminary ) 1997 Microchip Technology Inc. ...

Page 25

... When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector. 3: See Table 5-3 for reset value of specific condition Brown-out is enabled, else the BOR bit is unknown. 1997 Microchip Technology Inc. Power-on Reset MCLR Reset Brown-out Reset WDT Reset N ...

Page 26

... Microchip Technology Inc. ...

Page 27

... When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector. 3: See Table 5-3 for reset value of specific condition Brown-out is enabled, else the BOR bit is unknown. 1997 Microchip Technology Inc. Power-on Reset MCLR Reset Brown-out Reset ...

Page 28

... This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when V certain level such that < Preliminary EXTERNAL BROWN-OUT PROTECTION CIRCUIT 10k MCLR PIC17CXXX 40 k goes below DD EXTERNAL BROWN-OUT PROTECTION CIRCUIT MCLR PIC17CXXX below 0.7V V • Max Min Max Min Max Min. DD 1997 Microchip Technology Inc. ...

Page 29

... CA3IE TX2IF TX2IE RC2IF RC2IE 1997 Microchip Technology Inc. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which all vector to the same address) ...

Page 30

... When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled). PEIE T0CKIE T0IE INTE bit0 Preliminary R = Readable bit W = Writable bit - n = Value at POR reset 1997 Microchip Technology Inc. ...

Page 31

... Enable USART1 Transmit buffer empty interrupt 0 = Disable USART1 Transmit buffer empty interrupt RC1IE: USART1 Receive Interrupt Enable bit bit Enable USART1 Receive buffer full interrupt 0 = Disable USART1 Receive buffer full interrupt 1997 Microchip Technology Inc. CA1IE TX1IE RC1IE R = Readable bit W = Writable bit ...

Page 32

... Enable USART2 Transmit Interrupt 0 = Disable USART2 Transmit Interrupt RC2IE: USART2 Receive Interrupt Enable bit Enable USART2 Receive Interrupt 0 = Disable USART2 Receive Interrupt DS30264A-page CA4IE CA3IE TX2IE RC2IE bit0 Preliminary R = Readable bit W = Writable bit -n = Value at POR reset 1997 Microchip Technology Inc. ...

Page 33

... RC1IF: USART1 Receive Interrupt Flag bit (State controlled by hardware) bit USART1 Receive buffer is full 0 = USART1 Receive buffer is empty 1997 Microchip Technology Inc. Note: These bits will be set by the specified con- dition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts dis- abled) ...

Page 34

... USART2 Transmit buffer is full RC2IF: USART2 Receive Interrupt Flag (State controlled by hardware) bit USART2 Receive buffer is full 0 = USART2 Receive buffer is empty DS30264A-page CA4IF CA3IF TX2IF RC2IF bit0 2 C master mode Preliminary R = Readable bit W = Writable bit -n = Value at POR reset 1997 Microchip Technology Inc. ...

Page 35

... GLINTD bit. Note 2: Before disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled). 1997 Microchip Technology Inc. 6.5 RA0/INT Interrupt The external interrupt on the RA0/INT pin is edge trig- gered. Either the rising edge, if INTEDG bit (T0STA< ...

Page 36

... Q3 Q4 OSC1 OSC2 RA0/INT or RA1/T0CKI INTF or T0CKIF GLINTD System Bus Instruction PC Inst (PC) Inst (PC+1) Addr Fetched Instruction Inst (PC) executed DS30264A-page Addr (Vector) Inst (Vector) Addr RETFIE Inst (PC+1) Addr Addr Dummy Dummy Preliminary Inst ( Addr Dummy RETFIE 1997 Microchip Technology Inc. ...

Page 37

... UNBANK3, WREG MOVFP UNBANK2, BSR MOVFP UNBANK1, ALUSTA ; RETFIE 1997 Microchip Technology Inc. ; Address for 1st location to save ; Address for 2nd location to save ; Address for 3rd location to save ; Address for 4th location to save ; Address for 5th location to save ; (Label Not used in program) ...

Page 38

... Restore FSR value for other values ; ; Pop PCLATH value ; Pop WREG value ; FSR0 does not change ; Pop ALUSTA value ; Restore FSR value for other values ; ; Save the FSR for BSR values ; ; No Status bits are affected ; Return from interrupt (enable interrupts) Preliminary 1997 Microchip Technology Inc. ...

Page 39

... Note 1: User memory space may be internal, external, or both. The memory configuration depends on the processor mode. Preliminary 16 0000h 0008h 0010h 0018h 0020h 0021h 1FFFh (PIC17C752) 3FFFh (PIC17C756) FDFFh FE00h FE01h FE02h FE03h FE04h FE05h FE06h FE07h FE08h FE0Dh FE0Eh FE0Fh FE10h ...

Page 40

... External Program Memory PIC17C752 FFFFh OFF-CHIP 0000h External Program Memory PIC17C756 FFFFh OFF-CHIP 00h 120h FFh 1FFh ON-CHIP DS30264A-page 40 The PIC17C75X can operate in modes where the pro- gram memory is off-chip. They are the microprocessor and extended microcontroller modes. The micropro- cessor mode is the default for an unprogrammed device ...

Page 41

... Note 1: The access times for this requires the use of fast SRAMs. AD15-AD0 Memory (MSB) A15-A0 373 Ax-A0 D7- 373 (1) 138 Preliminary EPROM MEMORY ACCESS TIME ORDERING SUFFIX EPROM Suffix Cycle PIC17C752 ) PIC17C756 CY 500 ns -25 250 ns -15 200 ns -10 160 ns -70 121 ns (1) Memory (LSB) Ax-A0 D7-D0 CE (2) ( ...

Page 42

... The peripheral registers are in the banked portion of memory, while the core registers are in the unbanked region. To facilitate switching between the peripheral banks, the MOVLB bank instruction has been provided. Preliminary 1997 Microchip Technology Inc. ...

Page 43

... The upper nibble of the BSR specifies this bank. All other GPRs ignore the Bank Select Register (BSR) bits. 3: These RAM banks are not implemented on the PIC17C752. Reading any register in this bank reads ‘0’s 1997 Microchip Technology Inc. (1) (1) (1) ...

Page 44

... RC1/ RC0/ xxxx xxxx uuuu uuuu AD1 AD0 1111 1111 1111 1111 RD1/ RD0/ xxxx xxxx uuuu uuuu AD9 AD8 ---- 1111 ---- 1111 RE0/ALE ---- xxxx ---- uuuu TX1IF RC1IF x000 0010 u000 0010 TX1IE RC1IE 0000 0000 0000 0000 1997 Microchip Technology Inc. ...

Page 45

... The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 3: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset. 1997 Microchip Technology Inc. Bit 5 Bit 4 Bit 3 Bit 2 — ...

Page 46

... DC3 DC2 xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu PWM3ON -000 0000 -000 0000 — — ---- ---- ---- ---- xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 47

... RLCF) instructions, this bit is loaded with either the high or low order bit of the source register carry-out from the most significant bit of the result Note: For borrow the polarity is reversed. 1997 Microchip Technology Inc. affect any status bit. To see how other instructions affect the status bits, see the “Instruction Set Sum- mary.” ...

Page 48

... Note 1: The BOR status bit is a don’t care and is not necessarily brown-out circuit is disabled (when the BODEN bit in the Configuration word is programmed R R POR BOR bit0 Preliminary predictable if the R = Readable bit W = Writable bit U = Unimplemented bit, Read as ‘0’ Value at POR reset 0h (stack overflow). 1997 Microchip Technology Inc. ...

Page 49

... Unimplemented: Read as '0' bit 0: 1997 Microchip Technology Inc T0PS2 T0PS1 T0PS0 — bit0 ) CY Preliminary R = Readable bit W = Writable bit U = Unimplemented, reads as ‘0’ Value at POR reset ...

Page 50

... USART transmit reg- ister (TXREG). The starting address of the block of data to be transmitted could easily be modified by the program. FIGURE 7-9: INDIRECT ADDRESSING Instruction Executed Opcode Address Instruction Fetched Opcode File Preliminary 1997 Microchip Technology Inc. RAM File = INDFx FSR ...

Page 51

... INDF0 (or INDF1). If the source or destination of the indirect address is in banked memory, the location accessed will be deter- mined by the value in the BSR. 1997 Microchip Technology Inc. A simple program to clear RAM from 20h - FFh is shown in Example 7-1. EXAMPLE 7-1: ...

Page 52

... The following PC related operations do not change PCLATH: a) LCALL, RETLW, and RETFIE instructions. b) Interrupt vector is forced onto the PC Read-modify-write instructions on PCL (e.g. BSF PCL). Preliminary PCL ALU or destination PCL data bus ALU data bus PCL PCH PC<15:0> PC<12:0> PCLATH<4:0> 1997 Microchip Technology Inc. ...

Page 53

... Only Banks 0 through 7 are implemented. Selection of an unimplemented bank is not recommended. Bank 15 is reserved for Microchip use, reading of registers in this bank may cause random values to be read. 2: Bank 0 and Bank 1 are implemented for the PIC17C752, and Banks 0 through 3 are implemented for the PIC17C756. Selection of an unimplemented bank is not recommended. ...

Page 54

... NOTES: DS30264A-page 54 Preliminary 1997 Microchip Technology Inc. ...

Page 55

... TABLATL TLWT 1,f TLWT DATA MEMORY PROGRAM MEMORY f 1 Note 1: 8-bit value, from register 'f', loaded into the high or low byte in TABLAT (16-bit). 1997 Microchip Technology Inc. FIGURE 8-2: TABLE POINTER TABLE LATCH (16-bit) 3 TABLWT 1,i,f DATA MEMORY f 1 Note 1: 8-bit value, from register 'f', loaded into the high or low byte in TABLAT (16-bit) ...

Page 56

... Program Memory (TBLPTR) loaded into TABLAT register “i” then TBLPTR = TBLPTR + 1, If “i” then TBLPTR is unchanged. Preliminary TABLRD INSTRUCTION OPERATION TBLPTRL TABLATL 3 TABLRD 0,i,f PROGRAM MEMORY Prog-Mem (TBLPTR) 2 1997 Microchip Technology Inc. ...

Page 57

... Peripheral 1997 Microchip Technology Inc. 8.1.1 TERMINATING LONG WRITES An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the inter- rupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address ...

Page 58

... INST (PC+1) INST (PC+2) TABLWT cycle1 TABLWT cycle2 INST (PC+1) Data write cycle Flag bit, Do table write. Preliminary (for the next write Clear WDT ; address ; ; ; Load HI byte ; in TABLATH ; Load LO byte ; in TABLATH ; and write to ; program memory ; (Ext. SRAM) PC+2 1997 Microchip Technology Inc. ...

Page 59

... Instruction TABLWT1 TABLWT2 fetched Instruction TABLWT1 cycle1 TABLWT1 cycle2 TABLWT2 cycle1 TABLWT2 cycle2 INST (PC-1) executed ALE OE WR 1997 Microchip Technology Inc. TBL1 Data out 1 PC+2 TBL2 INST (PC+2) Data write cycle Data write cycle Preliminary Data out 2 PC+3 INST (PC+3) ...

Page 60

... Data read cycle TBL1 Data in 1 PC+2 TBL2 Data in 2 INST (PC+2) Data read cycle Data read cycle Preliminary ; address ; ; ; Dummy read, ; Updates TABLATH ; Read HI byte ; of TABLATH ; Read LO byte ; of TABLATH and ; Update TABLATH PC+2 PC+3 INST (PC+3) INST (PC+2) 1997 Microchip Technology Inc. ...

Page 61

... Hardware multiply signed Without hardware multiply Hardware multiply 1997 Microchip Technology Inc. Example 9-2 shows the sequence signed multiply. To account for the sign bits of the arguments, each argument’s most significant bit (MSb) is tested and the appropriate subtractions are done. ...

Page 62

... ARG2L MOVFP PRODL, WREG ; ADDWF RES1, F MOVFP PRODH, WREG ; ADDWFC RES2, F CLRF WREG, F ADDWFC RES3, F Preliminary UNSIGNED MULTIPLY ROUTINE ; ARG1L * ARG2L -> ; PRODH:PRODL ; ARG1H * ARG2H -> ; PRODH:PRODL ; ARG1L * ARG2H -> ; PRODH:PRODL ; Add cross products ; ; ; ; ARG1H * ARG2L -> ; PRODH:PRODL ; Add cross products ; ; ; 1997 Microchip Technology Inc. ...

Page 63

... MULTIPLICATION ALGORITHM RES3:RES0 = ARG1H:ARG1L ARG2H:ARG2L 16 = (ARG1H ARG2H (ARG1H ARG2L (ARG1L ARG2H 2 ) (ARG1L ARG2L) (-1 ARG2H<7> ARG1H:ARG1L 2 (-1 ARG1H<7> ARG2H:ARG2L 2 1997 Microchip Technology Inc. EXAMPLE 9-4: MOVFP ARG1L, WREG MULWF ARG2L MOVPF PRODH, RES1 ; MOVPF PRODL, RES0 ; ; MOVFP ARG1H, WREG MULWF ARG2H MOVPF PRODH, RES3 ...

Page 64

... NOTES: DS30264A-page 64 Preliminary 1997 Microchip Technology Inc. ...

Page 65

... A pin that is a peripheral input, can be con- figured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin. 1997 Microchip Technology Inc. 10.1 PORTA Register PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR). ...

Page 66

... OE = SPEN (SYNC+SYNC,CSRC) for RA5 Note: I/O pins have protection diodes to V Preliminary Peripheral data in Data Bus RD_PORTA (Q2 WR_PORTA Q CK (Q4) SDA out “1” SSP Mode . SS DIAGRAM Serial port input signal Data Bus RD_PORTA (Q2) Serial port output signals and 1997 Microchip Technology Inc. ...

Page 67

... Legend unknown unchanged unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc. Function Input or external interrupt input. Input or clock input to the TMR0 timer/counter, and/or an external interrupt input ...

Page 68

... PORTB is only used for the interrupt on change feature and key depression operations. Port Input Latch D Port Q Data Preliminary Peripheral Data in RBPU (PORTA<7>) Match Signal from other port pins RBIF Data Bus RD_DDRB (Q2) RD_PORTB (Q2 WR_DDRB (Q4) CK WR_PORTB (Q4) 1997 Microchip Technology Inc. ...

Page 69

... MOVLB instruction to load the BSR register for bank selection. FIGURE 10-6: BLOCK DIAGRAM OF RB3:RB2 PORT PINS Weak Pull-Up OE Note: I/O pins have protection diodes to V and Vss. DD 1997 Microchip Technology Inc. EXAMPLE 10-2: INITIALIZING PORTB MOVLB 0 ; Select Bank 0 CLRF PORTB ; Initialize PORTB by clearing ; ...

Page 70

... RBIF Data Bus RD_DDRB (Q2) RD_PORTB (Q2 WR_DDRB (Q4) CK WR_PORTB (Q4) SPI output SPI output enable Peripheral Data in (PORTA<7>) RBPU Match Signal from other port pins RBIF Data Bus RD_DDRB (Q2) RD_PORTB (Q2 WR_DDRB (Q4 output disable WR_PORTB (Q4) SPI output SPI output enable 1997 Microchip Technology Inc. ...

Page 71

... Legend unknown unchanged unimplemented read as '0 Value depends on condition. Shaded cells are not used by PORTB. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc. Function Input/Output or the Capture1 input pin. Software programmable weak pull-up and interrupt on change features. ...

Page 72

... Initialize PORTC data ; latches before setting ; the data direction register ; Value used to initialize ; data direction ; Set RC<3:0> as inputs ; RC<5:4> as outputs ; RC<7:6> as inputs to D_Bus IR INSTRUCTION READ Data Bus RD_PORTC WR_PORTC RD_DDRC WR_DDRC EX_EN DATA/ADDR_OUT SYS BUS Control DRV_SYS 1997 Microchip Technology Inc. ...

Page 73

... Data direction register for PORTC Legend unknown unchanged. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc. Function Input/Output or system bus address/data pin. Input/Output or system bus address/data pin. Input/Output or system bus address/data pin. ...

Page 74

... Initialize PORTD data ; latches before setting ; the data direction register ; Value used to initialize ; data direction ; Set RD<3:0> as inputs ; RD<5:4> as outputs ; RD<7:6> as inputs to D_Bus IR INSTRUCTION READ Data Bus RD_PORTD WR_PORTD RD_DDRD WR_DDRD EX_EN DATA/ADDR_OUT SYS BUS Control DRV_SYS 1997 Microchip Technology Inc. ...

Page 75

... Data direction register for PORTD Legend unknown unchanged. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc. Function Input/Output or system bus address/data pin. Input/Output or system bus address/data pin. Input/Output or system bus address/data pin. ...

Page 76

... Initialize PORTE data ; latches before setting ; the data direction ; register ; Value used to initialize ; data direction ; Set RE<1:0> as inputs ; RE<3:2> as outputs ; RE<7:4> are always ; read as '0' Data Bus RD_PORTE WR_PORTE RD_DDRE WR_DDRE EX_EN CNTL SYS BUS Control DRV_SYS 1997 Microchip Technology Inc. ...

Page 77

... CA4H Capture4 high byte 16h, Bank 7 TCON3 — CA4OVF Legend unknown unchanged unimplemented read as '0'. Shaded cells are not used by PORTE. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc Port CK ...

Page 78

... ADCON1 ; Digital CLRF PORTF ; Initialize PORTF data ; ; ; MOVLW 0x03 ; Value used to initialize ; MOVWF DDRF ; Set RF<1:0> as inputs ; other pads To other pads Preliminary latches before setting the data direction register data direction RF<7:2> as outputs I/O pin ST input buffer 1997 Microchip Technology Inc. ...

Page 79

... AN10 Legend unknown unchanged unimplemented read as '0'. Shaded cells are not used by PORTF. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. 1997 Microchip Technology Inc. Function Input/Output or analog input 4 Input/Output or analog input 5 Input/Output or analog input 6 ...

Page 80

... ADCON1 ; digital CLRF PORTG ; Initialize PORTG data ; ; ; MOVLW 0x03 ; Value used to initialize ; MOVWF DDRG ; Set RG<1:0> as inputs ; other pads To other pads Preliminary latches before setting the data direction register data direction RG<7:2> as outputs I/O pin ST input buffer 1997 Microchip Technology Inc. ...

Page 81

... FIGURE 10-15: RG4 BLOCK DIAGRAM Note: I/O pin has protection diodes to V and Vss. DD FIGURE 10-16: RG7:RG5 BLOCK DIAGRAM Note: I/O pins have protection diodes to V and Vss. DD 1997 Microchip Technology Inc Port Data Preliminary Peripheral Data In Data Bus RD_PORTG WR_PORTG ...

Page 82

... USART2 (SCI) Synchronous Clock. Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 RG5/ RG4/ RG3/ RG2/ RG1/ PWM3 CAP3 AN0 AN1 AN2 Preliminary Value on, Value on all Bit 0 POR, other resets BOR (Note1) 1111 1111 1111 1111 RG0/ xxxx 0000 uuuu 0000 AN3 1997 Microchip Technology Inc. ...

Page 83

... MOVWF PORTB MOVF PORTB,W fetched write to PORTB RB7:RB0 Instruction MOVWF PORTB executed write to PORTB 1997 Microchip Technology Inc. EXAMPLE 10-8: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT ; Initial PORT settings: PORTB<7:4> Inputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; ; ; ...

Page 84

... NOTES: DS30264A-page 84 Preliminary 1997 Microchip Technology Inc. ...

Page 85

... When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated if enabled. 1997 Microchip Technology Inc. 11.3 Timer2 Overview The Timer2 module is an 8-bit timer/counter with an 8-bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF fl ...

Page 86

... NOTES: DS30264A-page 86 Preliminary 1997 Microchip Technology Inc. ...

Page 87

... Unimplemented: Read as '0' bit 0: 1997 Microchip Technology Inc. (ADDRESS: 05h, UNBANKED T0PS2 T0PS1 T0PS0 ) CY Preliminary — Readable bit W = Writable bit bit0 U = Unimplemented, Read as '0' ...

Page 88

... Synchronization async ripple PSOUT counter T0PS3:T0PS0 (T0STA<4:1>) (note PSOUT is sampled here. Preliminary with the internal phase clocks. and 7T . Thus, for example, mea- OSC ( 121 MHz). OSC Interrupt on overflow sets T0IF (INTSTA<5>) TMR0H<8> TMR0L<8> (note 3) (note 1997 Microchip Technology Inc. ...

Page 89

... Fetch MOVFP W,TMR0L Instruction Write to TMR0L executed TMR0H 1997 Microchip Technology Inc. 12.3.2 WRITING A 16-BIT VALUE TO TMR0 Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H second in two consecutive instructions, as shown in Example 12-2 ...

Page 90

... Read TMR0L Read TMR0L Value on Value on all Bit 1 Bit 0 POR, other resets BOR (Note1) T0PS0 — 0000 000- 0000 000- POR BOR --11 1100 --11 qq11 T0IE INTE 0000 0000 0000 0000 xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 91

... TMR1CS: Timer1 Clock Source Select bit bit TMR1 increments off the falling edge of the RB4/TCLK12 pin 0 = TMR1 increments off the internal clock 1997 Microchip Technology Inc. Six other registers comprise the Capture2, Capture3, and Capture4 registers (CA2H:CA2L, CA3H:CA3L, and CA4H:CA4L). Figure 13-1, Figure 13-2, and Figure 13-3 are the con- ...

Page 92

... When T16 is set (in 16-bit Timer Mode Starts 16-bit TMR2:TMR1 0 = Stops 16-bit TMR2:TMR1 When T16 is clear (in 8-bit Timer Mode Starts 8-bit Timer1 0 = Stops 8-bit Timer1 DS30264A-page bit0 Preliminary R = Readable bit W = Writable bit -n = Value at POR reset 1997 Microchip Technology Inc. ...

Page 93

... Capture on every 16th rising edge PWM3ON: PWM3 On bit bit PWM3 is enabled (The RG5/PWM3 pin ignores the state of the DDRG<5> bit PWM3 is disabled (The RG5/PWM3 pin uses the state of the DDRG<5> bit for data direction) 1997 Microchip Technology Inc bit0 ...

Page 94

... For the external clock input timing requirements, see the Electrical Specification section. Reset TMR1 TMR1ON Comparator<8> Comparator x8 (TCON2<0>) Equal PR1 Reset TMR2 TMR2ON Comparator<8> Comparator x8 (TCON2<1>) Equal PR2 Preliminary Set TMR1IF (PIR1<4>) Set TMR2IF (PIR1<5>) 1997 Microchip Technology Inc. ...

Page 95

... Fosc/4 TMR1ON (TCON2<0>) TMR1CS (TCON1<0>) Set Interrupt TMR1IF (PIR1<4>) 1997 Microchip Technology Inc. 13.1.2.1 EXTERNAL CLOCK INPUT FOR TMR2:TMR1 When TMR1CS is set, the 16-bit TMR2:TMR1 incre- ments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchro- nized by the internal phase clocks twice every instruc- tion cycle ...

Page 96

... BOR --11 1100 --11 qq11 xxxx xxxx uuuu uuuu xxxx xxxx uuuu uuuu — xx-- ---- uu-- ---- — xx0- ---- uu0- ---- — xx0- ---- uu0- ---- DC2 xxxx xxxx uuuu uuuu DC2 xxxx xxxx uuuu uuuu DC2 xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 97

... In this example, PWM period = 50. Old duty cycle is 30. New duty cycle value is 10. 1997 Microchip Technology Inc. The user needs to set the PWM1ON bit (TCON2<4>) to enable the PWM1 output. When the PWM1ON bit is set, the RB2/PWM1 pin is confi ...

Page 98

... TMR2IF bit. These flags must be cleared in software. value from Preliminary PW1DCH, PW1DCL, PW2DCH, PWM FREQUENCY vs. RESOLUTION AT 33 MHz Frequency (kHz) 32.2 64.5 90.66 128.9 515.6 0x7F 0x5A 0x3F 0x0F 9-bit 8.5-bit 8-bit 6-bit 7-bit 6.5-bit 6-bit 4-bit 1997 Microchip Technology Inc. ...

Page 99

... Legend unknown unchanged unimplemented read as '0 value depends on conditions, shaded cells are not used by PWM Module. Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset. 1997 Microchip Technology Inc. 13.1.3.3.1 MAX RESOLUTION/FREQUENCY FOR EXTERNAL CLOCK INPUT ...

Page 100

... TMR3IF must be cleared in software. PR3H/CA1H PR3L/CA1L Comparator x16 Comparator<8> TMR3H TMR3L Capture2 Enable CA2H CA2L Set CA2IF (PIR1<3>) Capture3 Enable CA3H CA3L Set CA3IF (PIR2<2>) Capture4 Enable CA4H CA4L Set CA4IF (PIR2<3>) Preliminary Set TMR3IF (PIR1<6>) Equal Reset 1997 Microchip Technology Inc. ...

Page 101

... This may be useful during development phase to emulate a capture interrupt. 1997 Microchip Technology Inc. The input on the capture pin CAPx is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specifi ...

Page 102

... Section 13.2.1 for the operation of capture. TMR3H Capture1 Enable Set CA1IF (PIR1<2>) PR3H/CA1H PR3L/CA1L Capture2 Enable Set CA2IF (PIR1<3>) CA2H CA2L Capture3 Enable Set CA3IF (PIR2<2>) CA3H CA3L Capture4 Enable Set CA4IF (PIR2<3>) CA4H CA4L Preliminary 1997 Microchip Technology Inc. Set TMR3IF (PIR1<6>) TMR3L ...

Page 103

... Capture. Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset. 1997 Microchip Technology Inc. An example of an instruction sequence to read capture registers and capture overflow flag bits is shown in Example 13-1. Depending on the capture source, dif- ferent registers will need to be read ...

Page 104

... Disable interrupts ; ; ; Done, enable interrupts wreg 35h A8h MOVWF MOVFP MOVFP TMRx TMRx,W TMRx,W Write to TMRx Read TMRx Read TMRx indicates a sampling point. to timer increment is between 2Tosc and 6Tosc. Preliminary A9h 00h 'A9h' 1997 Microchip Technology Inc. ...

Page 105

... Read TMR1 Write TMR1 Read TMR1 TMR1 04h 05h 03h PR1 TMR1ON WR_TMR1 WR_TCON2 TMR1IF RD_TMR1 TMR1 reads 03h 1997 Microchip Technology Inc. BCF 3 BSF NOP MOVLB NOP TCON2, 0 TCON2, 0 Start TMR1 Stop TMR1 04h 05h 06h TMR1 reads 04h ...

Page 106

... NOTES: DS30264A-page 106 Preliminary 1997 Microchip Technology Inc. ...

Page 107

... Unimplemented: Read as '0' TRMT: Transmit Shift Register (TSR) Empty bit bit TSR empty 0 = TSR full TX9D: 9th bit of transmit data (can be used to calculated the parity in software) bit 0: 1997 Microchip Technology Inc. TABLE 14-1: USART MODULE GENERIC NAMES Generic name RCSTA TXSTA ...

Page 108

... USART configuration bits in the RCSTA and TXSTA registers. The bits that control I/O direction are: • SPEN • TXEN • SREN • CREN • CSRC — FERR OERR RX9D bit 0 Preliminary R = Readable bit W = Writable bit -n = Value at POR reset (x = unknown) 1997 Microchip Technology Inc. ...

Page 109

... FIGURE 14-3: USART TRANSMIT Sync/Async CK/TX Start TXREG FIGURE 14-4: USART RECEIVE OSC 4 BRG Master/Slave Buffer Logic CK SPEN Buffer Logic RX 1997 Microchip Technology Inc. BRG Sync/Async Sync/Async TSR Clock 7 8 Stop Load 8 Bit Count TXSTA<0> Data Bus TXIE Sync/Async Sync Bit Count ...

Page 110

... Desired Baud Rate Value on Value on all Bit 0 POR, other resets BOR (Note1) RX9D 0000 -00x 0000 -00u TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RX9D 0000 -00x 0000 -00u TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 111

... NA — HIGH 894.9 — LOW 3.496 — 1997 Microchip Technology Inc MHz OSC = 20 MHz SPBRG value %ERROR (decimal) KBAUD %ERROR — — NA — — — NA — — — NA — ...

Page 112

... F OSC = 32.768 kHz SPBRG value KBAUD %ERROR (decimal) 0.256 -14. — — NA — — NA — — NA — — NA — — NA — — NA — — NA — — 0.512 — 0 0.002 — 255 1997 Microchip Technology Inc. ...

Page 113

... TSR is empty. Note: The TSR is not mapped in data memory not available to the user. 1997 Microchip Technology Inc. Transmission is enabled TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 14-5) ...

Page 114

... TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RC2IF 000- 0010 000- 0010 RC2IE 000- 0000 000- 0000 RX9D 0000 -00x 0000 -00u xxxx xxxx uuuu uuuu TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 115

... CLK x16 CLK 1997 Microchip Technology Inc. Note: The FERR and the 9th receive bit are buff- ered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with val- ues for the next received Received data. ...

Page 116

... TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RC2IF 000- 0010 000- 0010 RC2IE 000- 0000 000- 0000 RX9D 0000 -00x 0000 -00u RX0 xxxx xxxx uuuu uuuu TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 117

... If either CREN or SREN are set during a transmission, the transmission is aborted and the RX/DT pin reverts to a hi-impedance state (for a recep- 1997 Microchip Technology Inc. tion). The TX/CK pin will remain an output if the CSRC bit is set (internal clock). The transmitter logic is not reset, although it is disconnected from the pins ...

Page 118

... TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RC2IF 000- 0010 000- 0010 RC2IE 000- 0000 000- 0000 RX9D 0000 -00x 0000 -00u TX0 xxxx xxxx uuuu uuuu TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu Word 2 bit6 bit7 1997 Microchip Technology Inc. ...

Page 119

... CREN bit RCIF bit Read RCREG Note: Timing diagram demonstrates SYNC master mode with SREN = 1. 1997 Microchip Technology Inc. Steps to follow when setting up a Synchronous Master Reception: 1. Initialize the SPBRG register for the appropriate baud rate. See Section 14.1 for details. ...

Page 120

... TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RC2IF 000- 0010 000- 0010 RC2IE 000- 0000 000- 0000 RX9D 0000 -00x 0000 -00u RX0 xxxx xxxx uuuu uuuu TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 121

... Microchip Technology Inc. 14.4.2 USART SYNCHRONOUS SLAVE RECEPTION Operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode. Also, SREN is a don't care in slave mode. ...

Page 122

... TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu RC2IF 000- 0010 000- 0010 RC2IE 000- 0000 000- 0000 RX9D 0000 -00x 0000 -00u RX0 xxxx xxxx uuuu uuuu TX9D 0000 --1x 0000 --1u xxxx xxxx uuuu uuuu 1997 Microchip Technology Inc. ...

Page 123

... Edge Select 2 Clock Select SSPM3:SSPM0 SMP:CKE 4 2 Edge Select Prescaler SCK 4, 16, 64 Data to TX/RX in SSPSR Data direction bit 1997 Microchip Technology Inc. FIGURE 15-2: I SCL SDA Internal data bus FIGURE 15-3: I SSPADD<6:0> 7 shift clock Baud Rate Generator SCL SDA TMR2 output ...

Page 124

... Data Transmit complete (does not include ACK and stop bits), SSPBUF is empty DS30264A-page 124 R-0 R-0 R-0 R mode only slave mode only) Preliminary R = Readable bit W = Writable bit bit0 U = Unimplemented bit, read as ‘0’ =Value at POR reset 1997 Microchip Technology Inc. ...

Page 125

... SPI slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin 2 0110 = I C slave mode, 7-bit address 2 0111 = I C slave mode, 10-bit address 2 1000 = I C master mode, clock = F 1xx1 = Reserved 1x1x = Reserved 1997 Microchip Technology Inc. R/W-0 R/W-0 R/W-0 R/W-0 SSPM3 SSPM2 SSPM1 SSPM0 bit0 2 C conditions were not valid for a ...

Page 126

... C slave mode only master mode only master mode only master mode only master mode only master mode only master mode only master mode only) Preliminary R = Readable bit W = Writable bit U = Unimplemented bit, Read as ‘0’ =Value at POR reset 1997 Microchip Technology Inc. ...

Page 127

... User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSP- BUF register completed successfully. 1997 Microchip Technology Inc. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT< ...

Page 128

... This leads to three scenarios for data transmission: T OSC • Master sends data — Slave sends dummy data • Master sends data — Slave sends data • Master sends dummy data — Slave sends data Preliminary 1997 Microchip Technology Inc. ...

Page 129

... Input Sample (SMP = 0) SDI (SMP = 1) bit7 Input Sample (SMP = 1) SSPIF SSPSR to SSPBUF 1997 Microchip Technology Inc. MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the fol- lowing: • ( OSC CY • F /16 (or 4 • T OSC CY • ...

Page 130

... The SSPIF bit in set after the last SCK edge. SPI Slave SSPM3:SSPM0 = 010xb SDO SDI SDI SDO LSb MSb Serial Clock SCK SCK Preliminary . DD Serial Input Buffer (SSPBUF) Shift Register (SSPSR) LSb PROCESSOR 2 1997 Microchip Technology Inc. ...

Page 131

... FIGURE 15-10: SLAVE SYNCHRONIZATION TIMING SS optional SCK (CKP = 0 CKE = 0) SCK (CKP = 1 CKE = 0) Write to SSPBUF SDO bit7 SDI (SMP = 0) bit7 Input Sample (SMP = 0) SSPIF Interrupt Flag SSPSR to SSPBUF 1997 Microchip Technology Inc. bit6 bit7 bit7 Preliminary bit0 bit0 DS30264A-page 131 ...

Page 132

... FIGURE 15-11: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) SS optional SCK (CKP = 0 CKE = 0) SCK (CKP = 1 CKE = 0) Write to SSPBUF SDO bit7 SDI (SMP = 0) bit7 Input Sample (SMP = 0) SSPIF Interrupt Flag SSPSR to SSPBUF DS30264A-page 132 bit6 bit2 bit5 bit4 bit3 Preliminary bit1 bit0 bit0 1997 Microchip Technology Inc. ...

Page 133

... SMP CKE Legend unknown unchanged unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset. 1997 Microchip Technology Inc. bit6 bit2 bit5 bit4 bit3 Bit 5 ...

Page 134

... Addr Match loaded (A7:A0). Set/Clear S bit and Clear/Set P, bits (SSPSTAT reg) and Set SSPIF Preliminary 2 C mode is enabled. The SSP module 2 C operation oper modes to be selected mode, with the SSPEN bit set, 1997 Microchip Technology Inc. ...

Page 135

... Transfer is Received BF SSPOV SSPSR 1997 Microchip Technology Inc. a) The SSPSR register value is loaded into the SSPBUF register. b) The buffer full bit set ACK pulse is generated. d) SSP interrupt flag bit, SSPIF (PIR2<7>) is set (interrupt is generated if enabled the falling edge of the ninth SCL pulse. ...

Page 136

... SSPBUF is written in software Set bit after writing to SSPBUF (the SSPBUF must be written-to before the CKP bit can be set) Preliminary Receiving Data ACK Bus Master terminates transfer ACK is not sent. Transmitting Data ACK From SSP interrupt service routine 1997 Microchip Technology Inc. ...

Page 137

... I 2 FIGURE 15-17: C SLAVE-TRANSMITTER (10-BIT ADDRESS) 1997 Microchip Technology Inc. Preliminary DS30264A-page 137 ...

Page 138

... FIGURE 15-18 SLAVE-RECEIVER (10-BIT ADDRESS) DS30264A-page 138 Preliminary 1997 Microchip Technology Inc. ...

Page 139

... S SSPIF (PIR2<7>) BF (SSPSTAT<0>) SSPOV (SSPCON1<6>) GCEN (SSPCON2<7>) 1997 Microchip Technology Inc. 15.2.2 GENERAL CALL ADDRESS SUPPORT The addressing procedure for the I the first byte after the START condition usually deter- mines which device will be the slave addressed by the master. The exception is the general call address which can address all devices ...

Page 140

... BOR (Note 1) INTE 0000 0000 0000 0000 RC2IF 00-- 0000 00-- 0000 RC2IE 00-- 0000 00-- 0000 0000 0000 0000 0000 xxxx xxxx uuuu uuuu SSPM0 0000 0000 0000 0000 SEN 0000 0000 0000 0000 BF 0000 0000 0000 0000 2 C mode. 1997 Microchip Technology Inc. ...

Page 141

... SSP hardware. FIGURE 15-20: SSP BLOCK DIAGRAM (I SDA SDA in SCL SCL in Bus Collision 1997 Microchip Technology Inc. The following events will cause SSP Interrupt Flag bit, SSPIF set (SSP Interrupt if enabled): • START condition • STOP condition • Data transfer byte transmitted/received 2 ...

Page 142

... The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF. 7. The user loads the SSPBUF with eight bits of data. 8. DATA is shifted out the SDA pin until all 8 bits are transmitted. Preliminary 1997 Microchip Technology Inc. Serial data operation. The baud ...

Page 143

... SCL is sampled high, reload takes place, and BRG starts its count. BRG reload Note: There are two baud rate overflows per clock period. Clock period may be of variable time due to clock arbitration. 1997 Microchip Technology Inc. 15.2.6 BAUD RATE GENERATOR ...

Page 144

... SSPCON2 is disabled until the START condition is complete. Set S bit (SSPSTAT<3>) At completion of start bit, automatic clear SSPCON2<0> T Write to SSPBUF occurs here BRG 2nd Bit 1st Bit T BRG T S BRG Preliminary 2 C module is reset into its IDLE state. 1997 Microchip Technology Inc. ...

Page 145

... FIGURE 15-24: START CONDITION FLOWCHART Bus collision detected, Set BCLIF, Release SCL, Clear SEN No Yes No SCL SCL = 0? Reset BRG 1997 Microchip Technology Inc. SSPEN = 1, SSPCON1<3:0> = 1000 Idle Mode SEN (SSPCON2<0> SDA = 1? SCL = 1? Yes Load BRG with SSPADD<6:0> No BRG SDA = 0? Rollover? Yes ...

Page 146

... Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the RESTART condition is complete. Set S (SSPSTAT<3>) SDA = 1, At completion of start bit, SCL = 1 automatic clear SSPCON2<1> BRG BRG BRG 1st Bit Write to SSPBUF occurs here. T BRG T BRG Sr = Restart Preliminary 1997 Microchip Technology Inc. ...

Page 147

... FIGURE 15-26: RESTART CONDITION FLOWCHART (PAGE 1) B Bus Collision, Set BCLIF, Release SDA, Clear RSEN 1997 Microchip Technology Inc. Start Idle Mode, SSPEN = 1, SSPCON1<3:0> = 1000 RSEN = 1(SSPCON2<1>) Force SCL = 0 No SCL = 0? Yes Release SDA, Load BRG with SSPADD<6:0> No BRG rollover? Yes ...

Page 148

... FIGURE 15-27: RESTART CONDITION FLOWCHART (PAGE 2) B DS30264A-page 148 C Yes SDA = 0? SCL = 1? Yes Reset BRG Force SDA = 0, Load BRG with SSPADD<6:0> No Force SCL = 0, Restart condition done, Preliminary A BRG rollover? Yes Set S, Set SSPIF BRG rollover? Yes Clear RSEN 1997 Microchip Technology Inc. ...

Page 149

... SSPIF is set, and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF leaving SCL low and SDA unchanged. (Figure 15-29) 1997 Microchip Technology Inc. 15.2.9.1 BF STATUS FLAG In transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out ...

Page 150

... Load BRG with SSPADD<6:0>, start BRG count No BRG rollover? Yes Force SCL = 1, Stop BRG No SCL = 1? Yes Load BRG with SSPADD<6:0>, count high time No Rollover? Yes Read SDA and place into AKSTAT bit (SSPCON2<6>) Force SCL = Set SSPIF 1997 Microchip Technology Inc. ...

Page 151

... FIGURE 15-29 MASTER MODE TIMING (TRANSMISSION 10-BIT ADDRESS) 1997 Microchip Technology Inc. Preliminary DS30264A-page 151 ...

Page 152

... WCOL STATUS FLAG If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn’t occur). bit, ACKEN Preliminary 1997 Microchip Technology Inc. ...

Page 153

... FIGURE 15-30: MASTER RECEIVER FLOWCHART 1997 Microchip Technology Inc. Idle mode RCEN = 1 Num_Clocks = 0, Release SDA Force SCL=0, Load BRG w/ SSPADD<6:0>, start count BRG No rollover? Yes Release SCL (Clock Arbitration) No SCL = 1? Yes Load BRG with SSPADD<6:0>, start count. No BRG rollover? Yes Sample SDA, ...

Page 154

... FIGURE 15-31 MASTER MODE TIMING (RECEPTION 7-BIT ADDRESS) DS30264A-page 154 Preliminary 1997 Microchip Technology Inc. ...

Page 155

... SSPIF Set SSPIF at the end of receive Note one baud rate generator period. BRG 1997 Microchip Technology Inc. 15.2.11.1 WCOL STATUS FLAG If the user writes the SSPBUF when an acknowledege bit, ACKEN sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn’t occur) ...

Page 156

... Yes Load BRG with SSPADD <6:0>, start count. DS30264A-page 156 BRG Yes rollover? No Yes Force SCL = 0, SCL = 0? Reset BRG Clear ACKEN No No ACKDT = 0? Yes Yes SDA = 1? No Bus collision detected, Set BCLIF, Release SCL, Clear ACKEN Preliminary 1997 Microchip Technology Inc. ...

Page 157

... Note one baud rate generator period. BRG 1997 Microchip Technology Inc. Whenever the CPU decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a Stop bit is detected (i ...

Page 158

... DS30264A-page 158 Start BRG No BRG rollover? Yes Release SDA, Start BRG No BRG rollover? Yes Bus Collision detected, No Set BCLIF, P bit Set? Clear SPEN Yes SDA going from while SCL = 1 Sets P bit SSPSTAT<4>, Set SSPIF, Stop Condition done Preliminary 1997 Microchip Technology Inc. ...

Page 159

... Release SCL, Slave device holds SCL low. to measure high time interval SCL SDA T BRG 1997 Microchip Technology Inc. When the SCL = 1 BRG starts counting clock high interval. SCL line sampled once every machine cycle (T Hold off BRG until SCL is sampled high. ...

Page 160

... S and P bits are cleared. Sample SDA. While SCL is high SDA line pulled low by another source data doesn’t match what is driven by the master. Bus collision has occurred. SDA released by master Set bus collision interrupt. Preliminary 2 C 1997 Microchip Technology Inc. ...

Page 161

... S bit and SSPIF set because BCLIF SDA = 0, SCL = 1 S SSPIF 1997 Microchip Technology Inc. If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 15-40). If however a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count ...

Page 162

... SDA = 1, SCL = 1 SEN BCLIF S SSPIF DS30264A-page 162 SDA = 0, SCL = BRG BRG SCL = 0 before SDA = 0, Bus collision occurs, Set BCLIF. SDA = 0, SCL = 1 Set S, SSPIF T Less than T BRG BRG S SDA = 0, SCL = 1 Set S, SSPIF Preliminary Interrupts cleared in software. Interrupts cleared in software. 1997 Microchip Technology Inc. ...

Page 163

... BCLIF Set BCLIF. Release SDA and SCL RSEN S SSPIF 1997 Microchip Technology Inc. reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time. If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, then a bus collision occurs ...

Page 164

... SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0'. (Figure 15-43 BRG BRG T BRG SCL goes low before SDA goes high Set BCLIF Preliminary SDA sampled T BRG low after T , BRG Set BCLIF T BRG 1997 Microchip Technology Inc. ...

Page 165

... R SDA SCL 2 NOTE devices with input levels related to V line to which the pull up resistor is also connected. 1997 Microchip Technology Inc The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the max- imum value of R (Figure 15-45). The SMP bit is the slew rate control enabled bit. This bit ...

Page 166

... NOTES: DS30264A-page 166 Preliminary 1997 Microchip Technology Inc. ...

Page 167

... ADON: A/D On bit bit A/D converter module is operating 0 = A/D converter module is shutoff and consumes no operating current 1997 Microchip Technology Inc. The A/D module has four registers. These registers are: • A/D Result High Register (ADRESH) • A/D Result Low Register (ADRESL) • ...

Page 168

... DS30264A-page 168 R/W-0 R/W-0 R/W-0 PCFG3 PCFG2 PCFG1 AN7 AN6 AN5 AN4 AN3 AN2 AN1 AN0 Digital I/O + and V - pins REF SS Preliminary R/W-0 PCFG0 R = Readable bit W = Writable bit bit0 U = Unimplemented bit, read as ‘0’ Value at POR reset 1997 Microchip Technology Inc. ...

Page 169

... FIGURE 16-3: A/D BLOCK DIAGRAM A/D Converter V - REF (Reference voltage REF 1997 Microchip Technology Inc. 2. Configure A/D interrupt (if desired): • Clear ADIF bit • Set ADIE bit • Clear GLINTD bit 3. Wait the required acquisition time. 4. Start conversion: • Set GO/DONE bit (ADCON0) 5 ...

Page 170

... During this time the holding capacitor is not connected to the selected A/D input channel Sampling Switch leakage V = 0.6V T 500 Preliminary . This calculation is ACQ ) has no REF ) is HOLD delay must complete before acqui- C HOLD = DAC capacitance = 200 Sampling Switch ( k ) 1997 Microchip Technology Inc. ...

Page 171

... For faster conversion times, the selection of another clock source is recommended. 4: When the device frequencies is greater than 1 MHz, the RC A/D conversion clock source is only recom- mended for sleep operation. 1997 Microchip Technology Inc. 16.2 Selecting the A/D Conversion Clock The A/D conversion time per bit is defined as T A/D conversion requires a minimum 12T conversion ...

Page 172

... After this 2T wait, acquisition on the selected channel is automati- cally started. The ADIF bit will be set and the GO/DONE bit is cleared upon completion of the A/D Conversion Preliminary and AV . The DD SS sample. That is, the wait is required AD AD 1997 Microchip Technology Inc. ...

Page 173

... RESULT 0000 00 ADRESH ADRESL 10-bits Right Justified 1997 Microchip Technology Inc. 16.5 A/D Operation During Sleep The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion ...

Page 174

... A. 000h , AD 16.10 References A good reference for the undestanding A/D converter is the "Analog-Digital Conversion Handbook" third edi- tion, published 0-13-03-2848-0). Preliminary for a Power-on Reset. The 1024 (Figure 16-6). REF Analog input voltage by Prentice Hall (ISBN 1997 Microchip Technology Inc. ...

Page 175

... A/D Result High Register 17h, Bank 5 Legend unknown unchanged unimplemented read as '0'. Shaded cells are not used for A/D conversion. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset. 1997 Microchip Technology Inc. Yes Finish Conversion SLEEP Instruction? ...

Page 176

... NOTES: DS30264A-page 176 Preliminary 1997 Microchip Technology Inc. ...

Page 177

... RC oscillator oscillator Reserved — 1997 Microchip Technology Inc. The PIC17CXXX has a Watchdog Timer which can be shutoff only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscil- lator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fi ...

Page 178

... The user can program two configuration bits (FOSC1:FOSC0) to select one of these four modes: • LF Low Power Crystal • XT Crystal/Resonator • EC External Clock Input • RC Resistor/Capacitor For information on the different oscillator types and how to use them, please refer to Section 4.0. Preliminary 1997 Microchip Technology Inc. ...

Page 179

... Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset. 2: This value will be as the device was programmed unprogrammed, will read as all '1's. 1997 Microchip Technology Inc. 17.3.2 CLEARING THE WDT AND POSTSCALER The WDT and postscaler are cleared when: • ...

Page 180

... This needs to be taken into account when OSC considering the interrupt response time when coming out of SLEEP Tost(2) Processor in SLEEP PC+1 PC+2 Inst (PC+1) SLEEP Preliminary Interrupt Latency (2) 0004h 0005h Inst (PC+2) Inst (PC+1) Dummy Cycle 1997 Microchip Technology Inc. ...

Page 181

... V . The contributions DD SS from on-chip pull-ups on PORTB should also be con- sidered, and disabled when possible. 1997 Microchip Technology Inc. 17.5 Code Protection The code in the program memory can be protected by selecting the microcontroller in code protected mode (PM2:PM0 = '000'). In this mode, instructions that are in the on-chip pro- gram memory space, can continue to read or write the program memory ...

Page 182

... MCLR/V MCLR DS30264A-page 182 For complete details of serial programming, please refer to the PIC17C75X Programming Specification. (Contact your local Microchip Technology Sales Office for availability.) FIGURE 17-4: TYPICAL IN-CIRCUIT SERIAL External Connector Signals + TEST CNTL . These IHH Dev. CLK pin. Also a ...

Page 183

... One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 25 MHz, the normal instruction execution time is 160 ns conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 320 ns. 1997 Microchip Technology Inc. TABLE 18-1: OPCODE FIELD DESCRIPTIONS Field Description Register fi ...

Page 184

... Q1 cycle. So there is no issue on doing R-M-W instructions on registers which contain these bits 0 ALUSTA will clear register PCH PCLATH; PCL dest PCLATH PCH; 8-bit destination value PCL PCL ALU operand PCLATH PCH; 8-bit result PCL 1997 Microchip Technology Inc. ...

Page 185

... Q cycles to the instruction cycle. FIGURE 18-2: Q CYCLE ACTIVITY Q1 Q2 Tosc Tcy1 1997 Microchip Technology Inc. The four Q cycles that make up an instruction cycle (Tcy) can be generalized as: Q1: Instruction Decode Cycle or forced No operation Q2: Instruction Read Cycle or No operation Q3: Process the Data ...

Page 186

... OV,C,DC,Z 0000 010d ffff ffff 1 OV,C,DC,Z 0000 001d ffff ffff 1 0001 110d ffff ffff 2 (3) 1010 10ti ffff ffff 2 1010 11ti ffff ffff 1997 Microchip Technology Inc. Notes Z None 3 Z None 6,8 None 2,6,8 None 2,6 None ...

Page 187

... Two-cycle instruction when condition is true, else single cycle instruction. 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles “skip” means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed. 1997 Microchip Technology Inc. Cycles 16-bit Opcode Status ...

Page 188

... ADDWF f 255 d [0,1] (WREG) + (f) (dest) OV, C, DC, Z 0000 111d ffff ffff Add WREG to register 'f the result is stored in WREG the result is stored back in register 'f Read Process Write to register 'f' Data destination ADDWF REG 0x17 = 0xC2 = 0xD9 = 0xC2 1997 Microchip Technology Inc. ...

Page 189

... REG 0 Before Instruction Carry bit = 1 REG = 0x02 WREG = 0x4D After Instruction Carry bit = 0 REG = 0x02 WREG = 0x50 1997 Microchip Technology Inc. ANDLW f,d Syntax: Operands: Operation: (dest) Status Affected: Encoding: ffff ffff Description: Words: Cycles: Q Cycle Activity: Q1 Decode Q4 Write to destination Example: ...

Page 190

... Q Cycle Activity: Q1 Decode Q4 Write to Example: destination Before Instruction FLAG_REG = 0xC7 After Instruction FLAG_REG = 0x47 Bit Clear f [ label ] BCF f 255 (f<b>) None 1000 1bbb ffff ffff Bit 'b' in register 'f' is cleared Read Process Write register 'f' Data register 'f' BCF FLAG_REG, 7 1997 Microchip Technology Inc. ...

Page 191

... Cycles Cycle Activity Decode Read Process register 'f' Data Example: BSF FLAG_REG, 7 Before Instruction FLAG_REG= 0x0A After Instruction FLAG_REG= 0x8A 1997 Microchip Technology Inc. BTFSC Syntax: Operands: Operation: Status Affected: Encoding: ffff ffff Description: Q4 Write Words: register 'f' Cycles: Q Cycle Activity: Q1 Decode If skip: ...

Page 192

... Q4 No operation Bit Toggle f [ label ] BTG f 255 0 b < 7 (f<b>) (f<b>) None 0011 1bbb ffff ffff Bit 'b' in data memory location 'f' is inverted Read Process Write register 'f' Data register 'f' BTG PORTC, 4 0111 0101 [0x75] 0110 0101 [0x65] 1997 Microchip Technology Inc. ...

Page 193

... operation operation operation Example: HERE CALL THERE Before Instruction PC = Address(HERE) After Instruction PC = Address(THERE) TOS = Address (HERE + 1) 1997 Microchip Technology Inc. CLRF Syntax: Operands: PC<12:0>, Operation: Status Affected: Encoding: kkkk kkkk Description: Words: Cycles: Q Cycle Activity: Q1 Decode Q4 Write to PC Example: Before Instruction ...

Page 194

... WREG Complement f [ label ] COMF f 255 d [0, (dest) Z 0001 001d ffff ffff The contents of register 'f' are comple- mented the result is stored in WREG the result is stored back in register 'f Read Process Write to register 'f' Data destination COMF REG1,0 = 0x13 = 0x13 = 0xEC 1997 Microchip Technology Inc. ...

Page 195

... NEQUAL : EQUAL : Before Instruction PC Address = HERE WREG = ? REG = ? After Instruction If REG = WREG Address (EQUAL) If REG WREG Address (NEQUAL) 1997 Microchip Technology Inc. CPFSGT f Syntax: Operands: Operation: Status Affected: Encoding: ffff ffff Description: Words: Cycles: Q Cycle Activity Decode operation If skip operation operation ...

Page 196

... BCD format) and produces a correct packed BCD result Result is placed in Data memory location 'f' and WREG Result is placed in Data memory location 'f Read Process Write register 'f' Data register 'f' and other specified register DAW REG1 0xA5 = ?? = 0x05 = 0x05 = 0xCE = ?? = 0x24 = 0x24 = 1997 Microchip Technology Inc. ...

Page 197

... Decode Read Process register 'f' Data Example: DECF CNT, 1 Before Instruction CNT = 0x01 After Instruction CNT = 0x00 1997 Microchip Technology Inc. DECFSZ Syntax: Operands: Operation: Status Affected: ffff ffff Encoding: Description: Q4 Write to Words: destination Cycles: Q Cycle Activity: Q1 Decode If skip operation Example: Before Instruction ...

Page 198

... The thirteen bit immediate value is loaded into PC bits <12:0>. Then the upper eight bits of PC are loaded into PCLATH. GOTO is always a two-cycle instruction Process Write to PC 'k' Data operation operation operation GOTO THERE 1997 Microchip Technology Inc. ...

Page 199

... Data Example: INCF CNT, 1 Before Instruction CNT = 0xFF After Instruction CNT = 0x00 1997 Microchip Technology Inc. INCFSZ Syntax: Operands: Operation: Status Affected: ffff ffff Encoding: Description: Q4 Words: Write to destination Cycles: Q Cycle Activity: Q1 Decode If skip operation Example: Before Instruction PC After Instruction ...

Page 200

... Inclusive OR Literal with WREG [ label ] IORLW 255 (WREG) .OR. (k) (WREG) Z 1011 0011 kkkk kkkk The contents of WREG are OR’ed with the eight bit literal 'k'. The result is placed in WREG Read Process Write to literal 'k' Data WREG IORLW 0x35 = 0x9A = 0xBF 1997 Microchip Technology Inc. ...