FAN3100CMPX Fairchild Semiconductor, FAN3100CMPX Datasheet - Page 2

FAN3100CMPX

Manufacturer Part Number

FAN3100CMPX

Description

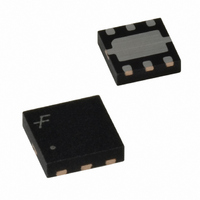

IC GATE DRVR SGL CMOS 2A 6MLP

Manufacturer

Fairchild Semiconductor

Type

Low Sider

Datasheet

1.FAN3100CSX.pdf

(22 pages)

Specifications of FAN3100CMPX

Configuration

Low-Side

Input Type

Differential

Delay Time

15ns

Current - Peak

3A

Number Of Configurations

1

Number Of Outputs

1

Voltage - Supply

4.5 V ~ 18 V

Operating Temperature

-40°C ~ 125°C

Mounting Type

Surface Mount

Package / Case

6-MLP

Rise Time

20 ns

Fall Time

14 ns

Supply Voltage (min)

4.5 V

Supply Current

0.35 mA

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Drivers

1

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

High Side Voltage - Max (bootstrap)

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

FAN3100CMPXTR

© 2007 Fairchild Semiconductor Corporation

FAN3100 • Rev. 1.0.3

Ordering Information

FAN3100CMPX

FAN3100CSX

FAN3100TMPX

FAN3100TSX

Package Outlines

Thermal Characteristics

6-Lead 2x2mm Molded Leadless Package (MLP)

SOT23-5

Notes:

1.

2.

3.

4.

5.

6.

Part Number

Estimates derived from thermal simulation; actual values depend on the application.

Theta_JL (

thermal pad) that are typically soldered to a PCB.

Theta_JT (

held at a uniform temperature by a top-side heatsink.

Theta_JA (Θ

The value given is for natural convection with no heatsink using a 2SP2 board, as specified in JEDEC standards JESD51-2,

JESD51-5, and JESD51-7, as appropriate.

Psi_JB (

application circuit board reference point for the thermal environment defined in Note 4. For the MLP-6 package, the board

reference is defined as the PCB copper connected to the thermal pad and protruding from either end of the package. For the

SOT23-5 package, the board reference is defined as the PCB copper adjacent to pin 2.

Psi_JT (

the center of the top of the package for the thermal environment defined in Note 4.

Figure 3. 2x2mm 6-Lead MLP (Top View)

JB

JT

): Thermal characterization parameter providing correlation between the semiconductor junction temperature and

): Thermal characterization parameter providing correlation between semiconductor junction temperature and an

JL

JT

JA

): Thermal resistance between the semiconductor junction and the bottom surface of all the leads (including any

): Thermal resistance between the semiconductor junction and the top surface of the package, assuming it is

): Thermal resistance between junction and ambient, dependent on the PCB design, heat sinking, and airflow.

Threshold

Package

CMOS

CMOS

Input

TTL

TTL

(1)

6-Lead 2x2mm MLP

5-Pin SOT23

6-Lead 2x2mm MLP

5-Pin SOT23

Package

2

2.7

56

JL

(2)

Packing Method

Figure 4. SOT23-5 (Top View)

133

JT

99

Tape & Reel

Tape & Reel

Tape & Reel

Tape & Reel

(3)

157

JA

58

(4)

2.8

JB

51

(5)

Quantity / Reel

42

JT

5

3000

3000

3000

3000

(6)

www.fairchildsemi.com

Units

°C/W

°C/W