DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 178

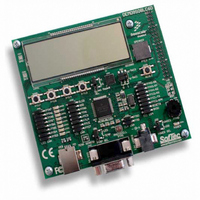

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 178 of 360

- Download datasheet (4Mb)

Chapter 10 Internal Clock Generator (S08ICGV4)

10.4.3

178

Reset

REFST

CLKST

ERCS

LOCK

LOCS

ICGIF

LOLS

Field

7:6

5

4

3

2

1

0

W

R

ICG Status Register 1 (ICGS1)

Clock Mode Status — The CLKST bits indicate the current clock mode. The CLKST bits don’t update

immediately after a write to the CLKS bits due to internal synchronization between clock domains.

00 Self-clocked

01 FLL engaged, internal reference

10 FLL bypassed, external reference

11 FLL engaged, external reference

Reference Clock Status — The REFST bit indicates which clock reference is currently selected by the

Reference Select circuit.

0 External Clock selected.

1 Crystal/Resonator selected.

FLL Loss of Lock Status — The LOLS bit is a sticky indication of FLL lock status.

0 FLL has not unexpectedly lost lock since LOLS was last cleared.

1 FLL has unexpectedly lost lock since LOLS was last cleared, LOLRE determines action taken.FLL has

FLL Lock Status — The LOCK bit indicates whether the FLL has acquired lock. The LOCK bit is cleared in off,

self-clocked, and FLL bypassed modes.

0 FLL is currently unlocked.

1 FLL is currently locked.

Loss Of Clock Status — The LOCS bit is an indication of ICG loss of clock status.

0 ICG has not lost clock since LOCS was last cleared.

1 ICG has lost clock since LOCS was last cleared, LOCRE determines action taken.

External Reference Clock Status — The ERCS bit is an indication of whether or not the external reference

clock (ICGERCLK) meets the minimum frequency requirement.

0 External reference clock is not stable, frequency requirement is not met.

1 External reference clock is stable, frequency requirement is met.

ICG Interrupt Flag — The ICGIF read/write flag is set when an ICG interrupt request is pending. It is cleared by

a reset or by reading the ICG status register when ICGIF is set and then writing a logic 1 to ICGIF. If another ICG

interrupt occurs before the clearing sequence is complete, the sequence is reset so ICGIF would remain set after

the clear sequence was completed for the earlier interrupt. Writing a logic 0 to ICGIF has no effect.

0 No ICG interrupt request is pending.

1 An ICG interrupt request is pending.

0

7

unexpectedly lost lock since LOLS was last cleared, LOLRE determines action taken.

CLKST

= Unimplemented or Reserved

0

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 10-3. ICGS1 Register Field Descriptions

Figure 10-8. ICG Status Register 1 (ICGS1)

REFST

0

5

LOLS

0

4

Description

LOCK

3

0

LOCS

0

2

Freescale Semiconductor

ERCS

0

1

ICGIF

1

0

0

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: