DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 340

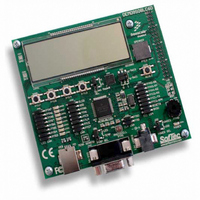

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 340 of 360

- Download datasheet (4Mb)

Appendix A Electrical Characteristics

340

1

2

3

4

5

6

7

8

Duty cycle of input clock

Output clock ICGOUT frequency

Minimum DCO clock (ICGDCLK) frequency

Maximum DCO clock (ICGDCLK) frequency

Self-clock mode (ICGOUT) frequency

Self-clock mode reset (ICGOUT) frequency

Loss of reference frequency

Loss of DCO frequency

Crystal start-up time

FLL lock time

FLL frequency unlock range

FLL frequency lock range

ICGOUT period jitter,

Internal oscillator deviation from trimmed frequency

Self-clocked mode frequency is the frequency that the DCO generates when the FLL is open-loop.

Loss of reference frequency is the reference frequency detected internally, which transitions the ICG into self-clocked

mode if it is not in the desired range.

Loss of DCO frequency is the DCO frequency detected internally, which transitions the ICG into FLL bypassed external

mode (if an external reference exists) if it is not in the desired range.

This parameter is characterized before qualification rather than 100% tested.

Proper PC board layout procedures must be followed to achieve specifications.

This specification applies to the period of time required for the FLL to lock after entering FLL engaged internal or external

modes. If a crystal/resonator is being used as the reference, this specification assumes it is already running.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f

Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise

injected into the FLL circuitry via V

percentage for a given interval.

See

CLKS = 10, REFS = 0

All other cases

Low range

High range

Low range

High range

Low range

High range

Long term jitter (averaged over 2 ms interval)

V

V

DD

DD

Figure A-10

= 1.8 – 3.6 V, (constant temperature)

= 3.0 V ±10%, –40° C to 85° C

4, (6)

(V

DDA

Characteristic

(4), (5)

4, (7)

= V

(3)

measured at f

DDA

4

(2)

(REFS = 0)

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

(min) to V

Table A-12. ICG Frequency Specifications

DDA

(1)

ICGOUT

and V

DDA

SSA

Max

(max), Temperature Range = 0 to 70°C Ambient)

and variation in crystal oscillator frequency increase the C

(8)

f

f

ICGDCLKmax

ICGDCLKmin

f

Symbol

f

Self_reset

n

ACC

ICGOUT

t

t

C

t

n

t

CSTH

f

f

CSTL

Lockh

Unlock

f

Lockl

LOR

LOD

t

Self

Lock

Jitter

dc

int

f

f

ICGDCLKmin

Extal

f

lo

–4*N

–2*N

Min

5.5

0.5

40

(min)

50

—

—

—

—

—

—

—

8

5

(min)

Typical

± 0.5

±0.5

430

—

—

—

8

4

Freescale Semiconductor

f

f

f

ICGDCLKmax

ICGDCLKmax

Extal

(max)

Max

10.5

500

4*N

2*N

1.5

0.2

60

40

25

±2

±2

—

—

5

5

(max)

Jitter

counts

counts

% f

ICGOUT

MHz

MHz

MHz

MHz

MHz

MHz

Unit

kHz

ms

ms

%

%

ICG

.

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: