DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 181

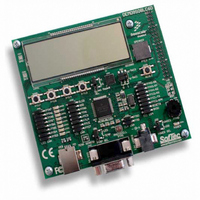

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 181 of 360

- Download datasheet (4Mb)

10.5.1

Normally when the CPU enters stop mode, the ICG will cease all clock activity and is in the off state.

However there are two cases to consider when clock activity continues while the CPU is in stop mode,

10.5.1.1 BDM Active

When the BDM is enabled, the ICG continues activity as originally programmed. This allows access to

memory and control registers via the BDC controller.

10.5.1.2 OSCSTEN Bit Set

When the oscillator is enabled in stop mode (OSCSTEN = 1), the individual clock generators are enabled

but the clock feed to the rest of the MCU is turned off. This option is provided to avoid long oscillator

startup times if necessary, or to run the RTI from the oscillator during stop3.

10.5.1.3 Stop/Off Mode Recovery

Upon the CPU exiting stop mode due to an interrupt, the previously set control bits are valid and the system

clock feed resumes. If FEE is selected, the ICG will source the internal reference until the external clock

is stable. If FBE is selected, the ICG will wait for the external clock to stabilize before enabling ICGOUT.

Upon the CPU exiting stop mode due to a reset, the previously set ICG control bits are ignored and the

default reset values applied. Therefore the ICG will exit stop in SCM mode configured for an

approximately 8 MHz DCO output (4 MHz bus clock) with trim value maintained. If using a crystal, 4096

clocks are detected prior to engaging ICGERCLK. This is incorporated in crystal start-up time.

10.5.2

Self-clocked mode (SCM) is the default mode of operation and is entered when any of the following

conditions occur:

In this state, the FLL loop is open. The DCO is on, and the output clock signal ICGOUT frequency is given

by f

into the filter registers (ICGFLTH and ICGFLTL). This is the only mode in which the filter registers can

be written.

If this mode is entered due to a reset, f

mode is entered from FLL engaged internal, f

is entered from FLL engaged external (either by programming CLKS or due to a loss of external reference

clock), f

If this mode is entered from off mode, f

Freescale Semiconductor

•

•

•

•

ICGDCLK

After any reset.

Exiting from off mode when CLKS does not equal 10. If CLKS = X1, the ICG enters this state

temporarily until the DCO is stable (DCOS = 1).

CLKS bits are written from X1 to 00.

CLKS = 1X and ICGERCLK is not detected (both ERCS = 0 and LOCS = 1).

ICGDCLK

Off Mode (Off)

Self-Clocked Mode (SCM)

/ R. The ICGDCLK frequency can be varied from 8 MHz to 40 MHz by writing a new value

will maintain the previous frequency, but ICGOUT will double if the FLL was unlocked.

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

ICGDCLK

ICGDCLK

ICGDCLK

will default to f

will be equal to the frequency of ICGDCLK before

will maintain the previous frequency.If this mode

Self_reset

Chapter 10 Internal Clock Generator (S08ICGV4)

which is nominally 8 MHz. If this

181

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: