ATMEGA640-16CU Atmel, ATMEGA640-16CU Datasheet - Page 37

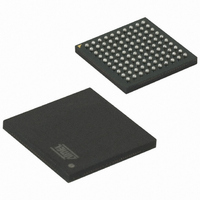

ATMEGA640-16CU

Manufacturer Part Number

ATMEGA640-16CU

Description

IC MCU AVR 64K FLASH 100-CBGA

Manufacturer

Atmel

Series

AVR® ATmegar

Specifications of ATMEGA640-16CU

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

EBI/EMI, I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

86

Program Memory Size

64KB (32K x 16)

Program Memory Type

FLASH

Eeprom Size

4K x 8

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 16x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

ATMEGA64x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

8 KB

Interface Type

2-Wire, SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

86

Number Of Timers

6

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 16 Channel

For Use With

ATSTK600-TQFP100 - STK600 SOCKET/ADAPTER 100-TQFP770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAGATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK503 - STARTER KIT AVR EXP MODULE 100P

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 37 of 444

- Download datasheet (10Mb)

8.3

8.3.1

8.3.2

8.3.3

8.4

8.4.1

2549M–AVR–09/10

General Purpose registers

External Memory registers

GPIOR2 – General Purpose I/O Register 2

GPIOR1 – General Purpose I/O Register 1

GPIOR0 – General Purpose I/O Register 0

XMCRA – External Memory Control Register A

• Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct

address is set up in the EEAR Register, the EERE bit must be written to a logic one to trigger the

EEPROM read. The EEPROM read access takes one instruction, and the requested data is

available immediately. When the EEPROM is read, the CPU is halted for four cycles before the

next instruction is executed.

The user should poll the EEPE bit before starting the read operation. If a write operation is in

progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

• Bit 7 – SRE: External SRAM/XMEM Enable

Writing SRE to one enables the External Memory Interface.The pin functions AD7:0, A15:8,

ALE, WR, and RD are activated as the alternate pin functions. The SRE bit overrides any pin

direction settings in the respective data direction registers. Writing SRE to zero, disables the

External Memory Interface and the normal pin and data direction settings are used.

• Bit 6:4 – SRL2:0: Wait-state Sector Limit

It is possible to configure different wait-states for different External Memory addresses. The

external memory address space can be divided in two sectors that have separate wait-state bits.

The SRL2, SRL1, and SRL0 bits select the split of the sectors, see

Bit

0x2B (0x4B)

Read/Write

Initial Value

Bit

0x2A (0x4A)

Read/Write

Initial Value

Bit

0x1E (0x3E)

Read/Write

Initial Value

Bit

“(0x74)”

Read/Write

Initial Value

MSB

MSB

MSB

R/W

R/W

R/W

SRE

R/W

7

0

7

0

7

0

7

0

SRL2

R/W

R/W

R/W

R/W

6

0

6

0

6

0

6

0

ATmega640/1280/1281/2560/2561

SRL1

R/W

R/W

R/W

R/W

5

0

5

0

5

0

5

0

SRL0

R/W

R/W

R/W

R/W

4

0

4

0

4

0

4

0

SRW11

R/W

R/W

R/W

R/W

3

0

3

0

3

0

3

0

SRW10

R/W

R/W

R/W

R/W

2

0

2

0

2

0

2

0

Table 8-2 on page 38

SRW01

R/W

R/W

R/W

R/W

1

0

1

0

1

0

1

0

SRW00

LSB

LSB

LSB

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

GPIOR2

GPIOR1

GPIOR0

XMCRA

and

37

Related parts for ATMEGA640-16CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 64K FLASH 100-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 64K FLASH 16MHZ 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 64K FLASH 16MHZ 100CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 64K 16MHZ 5V 64TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 64K 16MHZ 5V 64-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 64K 16MHZ COM 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 64K 16MHZ IND 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 64K 16MHZ COM 64-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 64KB FLASH 16MHZ 64TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 64KB FLASH 16MHZ 64QFN

Manufacturer:

Atmel

Datasheet: