COP8SAA720N9 National Semiconductor, COP8SAA720N9 Datasheet - Page 39

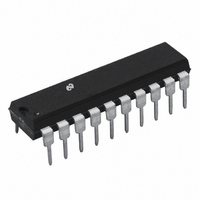

COP8SAA720N9

Manufacturer Part Number

COP8SAA720N9

Description

IC MCU OTP 8BIT 1K 20DIP

Manufacturer

National Semiconductor

Series

COP8™ 8SAr

Datasheet

1.COP8-PGMA-28CSP.pdf

(60 pages)

Specifications of COP8SAA720N9

Core Processor

COP8

Core Size

8-Bit

Speed

10MHz

Connectivity

Microwire/Plus (SPI)

Peripherals

POR, PWM, WDT

Number Of I /o

16

Program Memory Size

1KB (1K x 8)

Program Memory Type

OTP

Ram Size

64 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

20-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Other names

*COP8SAA720N9

COP8SAA720N9B

COP8SAA720NB

COP8SAA720N9B

COP8SAA720NB

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

64 On-Chip RAM Bytes.

(COP8SAAx)

128 On-Chip RAM Bytes

(COP8SABx/SACx)

Reading any undefined memory location in the address range of 0080H–00FFH will return undefined data.

12.0 Memory Map

All RAM, ports and registers (except A and PC) are mapped into data memory address space.

Select

RAM

ADD REG

DD to DF

CB to CF

Address

A0 to C6

E0 to E5

F0 to FB

02 to 2F

30 to 7F

00 to 6F

70 to 7F

80 to 93

CA

DA

DB

DC

EC

ED

C7

C8

C9

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

EA

EB

EE

EF

FC

FD

FE

94

95

96

97

E6

E7

E8

E9

FF

39

On-Chip RAM (48 Bytes)

Unused RAM (Reads as all ones)

On-Chip RAM (112 Bytes)

Unused RAM (Reads as all ones)

Reserved

Port F Data Register

Port F Configuration Register

Port F Input Pins (Read Only)

Reserved

Reserved

WATCHDOG Service Register (Reg: WDSVR)

MIWU Edge Select Register (Reg: WKEDG)

MIWU Enable Register (Reg: WKEN)

MIWU Pending Register (Reg: WKPND)

Reserved

Port L Data Register

Port L Configuration Register

Port L Input Pins (Read Only)

Reserved

Port G Data Register

Port G Configuration Register

Port G Input Pins (Read Only)

Reserved

Port C Data Register

Port C Configuration Register

Port C Input Pins (Read Only)

Reserved

Port D

Reserved

Reserved

Timer T1 Autoload Register T1RB Lower Byte

Timer T1 Autoload Register T1RB Upper Byte

ICNTRL Register

MICROWIRE/PLUS Shift Register

Timer T1 Lower Byte

Timer T1 Upper Byte

Timer T1 Autoload Register T1RA Lower Byte

Timer T1 Autoload Register T1RA Upper Byte

CNTRL Control Register

PSW Register

On-Chip RAM Mapped as Registers

X Register

SP Register

B Register

Reserved (Segment Register)

Contents

www.national.com