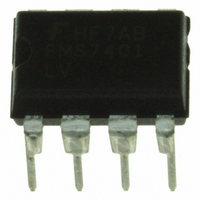

FMS7401LVN Fairchild Semiconductor, FMS7401LVN Datasheet - Page 42

FMS7401LVN

Manufacturer Part Number

FMS7401LVN

Description

IC CTRLR POWER DGTL EEPROM 8DIP

Manufacturer

Fairchild Semiconductor

Datasheet

1.FMS7401LVN.pdf

(81 pages)

Specifications of FMS7401LVN

Applications

Digital Power Controller

Core Processor

8-Bit

Program Memory Type

EEPROM (1 kB)

Ram Size

64 x 8

Number Of I /o

6

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 125°C

Mounting Type

Through Hole

Package / Case

8-DIP (0.300", 7.62mm)

Output Current

5 mA

Input Voltage

2.7 V to 3.6 V

Switching Frequency

2 MHz

Operating Temperature Range

- 40 C to + 125 C

Mounting Style

Through Hole

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Interface

-

Controller Series

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

FMS7401LVN_NL

FMS7401LVN_NL

FMS7401LVN_NL

FMS7401L

issue a system reset unless the feature is enabled by the Watchdog Enable (WDEN) bit of the Initialization Register 1.

WDEN bit can only be set while the device is in programming mode.

always power-up enabled. Software cannot disable Watchdog Resets. The Watchdog Reset can only be disabled in program-

ming mode by clearing the WDEN bit as long as the memory write protect (WDIS) feature is not enabled.

The Watchdog Timer is a 4-bit extension of the Timer 0’s main 12-bit up-counter. With each overflow of the main counter, the

Watchdog Timer extension bits may increment to a count of 16. If the Watchdog Timer is allowed to increment to the 16

count, a Watchdog Reset is issued triggering a system reset. The system reset will initialize all device circuits and instruction

execution will restart at the default program counter address (0xC00) after T

In order to service the Watchdog Timer to prevent a reset, software must write 0x1B to the Watchdog Service Register

(WDSVR) before every 61,440 cycles (the 16

Watchdog Timer count) since the last Watchdog Timer service or system reset. Once the Watchdog Timer is serviced, the 4-bit

Watchdog Timer is cleared and then continues to increment. The Watchdog Timer will issue a reset if it is serviced too fre-

quently or not frequently enough where the servicing of the Watchdog Timer is controlled completely by software.

The Watchdog Timer, like Timer 0’s counter, is not memory mapped and cannot be accessed by software. Software must

monitor the Watchdog Timer by keeping a count of the number of T0PND flags since the last service or reset. If software clears

the T0PND flags before the next Timer 0 counter overflow, software may count the number of triggered T0PND flags in order

to determine when to next service the Watchdog Timer. The Watchdog Timer remains operational during Idle Mode; therefore,

software should service the Watchdog Timer prior to entering Idle Mode to prevent false resets.

It is not recommended to service the Watchdog Timer within an interrupt service routine (ISR). For example, the most obvious

place to issue the Watchdog service command seems to be within the Timer 0 ISR since it guarantees the Watchdog Timer ser-

vice to occur within the allowed 4,096-61,440 cycle window. However, this action takes place automatically since the Timer 0

circuit runs independently from the microcontroller program execution without knowledge of the state of the microcontroller

core. If the program execution is stuck in an infinite loop due to some unforeseen circumstances, the TMRI0 hardware interrupt

will still be triggered executing software’s ISR, the Watchdog Timer will then be serviced, and program execution will return to

the infinite loop once the ISR completes. The infinite loop or “runaway condition” will continue undetected defeating the pur-

pose of the Watchdog Reset feature. The ISRs may be used to keep track of the number of cycles since the last Watchdog ser-

vice (e.g. keep a count of the number of T0PND flags triggered). However, the actual Watchdog service command must be

issued within software’s main program code.

Table 19. Watchdog Service Register (WDSVR) Definition

1. Refer to

2. Hardware interrupts are not executed by the microcontroller core unless the Global Interrupt enable (G) flag of the Status register is set. Refer to the

3. The Timer 0 hardware interrupt will be executed in the defined priority order. Refer to the

4. After a system reset, the T0CNTRL register is defaulted to 0x00.

5. Refer to the

6. Refer to the

7. The FMS7401L must be placed in a special programming mode in order to have full write and read access of all of the device memories. Refer to the

8. Refer to the

42

controller Core

Programming Specification

Bit 7

0

Table 30

Power Saving Modes

Device Memory

Electrical Characteristics

section of the datasheet for details.

of the

Device Memory

section of the datasheet for details.

Bit 6

section of the datasheet for details regarding the Initialization Registers.

0

section of the datasheet for Idle Mode wakeup conditions.

section of the datasheet for details.

section of the datasheet for the detailed memory map.

Bit 5

0

th

Watchdog Timer count) and not earlier than the first 4,096 cycles (the 1

WDSVR (addr. 0xB5)

Bit 4

1

7

Bit 3

If set, the Watchdog Timer’s system reset ability will

1

8-Bit Microcontroller Core

RESET

delay.

Bit 2

0

8

section of the datasheet for details.

PRODUCT SPECIFICATION

Bit 1

1

REV. 1.0.3 1/24/05

Bit 0

8-Bit Micro-

In-circuit

6

1

st

The

th