NM34C02M8X Fairchild Semiconductor, NM34C02M8X Datasheet

NM34C02M8X

Related parts for NM34C02M8X

NM34C02M8X Summary of contents

Page 1

... Block Diagram SDA SCL © 1999 Fairchild Semiconductor Corporation NM34C02 Rev. D.2 Features Extended Operating Voltage: 2.7V-5.5V Write-Protection for first 128 bytes 200 A active current typical – standby current typical – 1.0 A standby current typical (L) – 0.1 A standby current typical (LZ) IIC compatible interface – ...

Page 2

Connection Diagram Ordering Information NM34C02 NM34C02 Rev. D.2 SO (M8) and TSSOP (MT8) Package NM34C02 SCL SDA DS012821-2 Top View See ...

Page 3

Product Specifications Absolute Maximum Ratings Ambient Storage Temperature All Input or Output Voltages with Respect to Ground Lead Temperature (Soldering, 10 seconds) ESD Rating Standard V (4.5V to 5.5V) DC Electrical Characteristics CC Symbol Parameter I Active Power Supply Current ...

Page 4

AC Conditions of Test Input Pulse Levels V CC Input Rise and Fall Times 10 ns Input & Output Timing Levels V CC Output Load 1 TTL Gate and C Read and Write Cycle Limits (Standard and Low V Symbol ...

Page 5

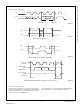

Bus Timing SCL t SU:STA SDA IN SDA OUT Background Information (IIC Bus) As mentioned, the IIC bus allows synchronous bidirectional com- munication between Transmitter/Receiver using the SCL (clock) and SDA (Data I/O) lines. All communication must be started with ...

Page 6

Device NM34C02 Pin Descriptions Serial Clock (SCL) The SCL input is used to clock all data into and out of the device. Serial Data (SDA) SDA is a bidirectional pin used to transfer data into and out of the device. ...

Page 7

Write Cycle Timing SCL SDA WORD n SCL SDA SCL CONDITION SDA SCL FROM MASTER DATA OUTPUT FROM TRANSMITTER DATA OUTPUT FROM RECEIVER Acknowledge Responses from Receiver (Figure 3). Device Addressing Following a start condition the master must output the ...

Page 8

Device Addressing (Continued) Device Type Device Identifier Address NM34C02 Slave Addresses (Figure 4). Refer to the following table for Slave Address string details: Device Page Blocks NM34C02 ...

Page 9

Write Protect Scheme (Continued) Bus Activity: Master R SDA Line S T SLAVE A Bus Activity: ADDRESS R Master T SDA Line Bus Activity: Master SDA Line Bus Activity: Read Operations Read operations are initiated in the same manner as ...

Page 10

Read Operations (Continued) operations increments all word address bits, allowing the entire memory contents to be serially read during one operation. After the entire memory has been read, the counter 'rolls over' and the NM34C02 continues to output data for ...

Page 11

Physical Dimensions inches (millimeters) unless otherwise noted 0.150 - 0.157 (3.810 - 3.988) 0.010 - 0.020 x 45 (0.254 - 0.508) 0.04 0.0075 - 0.0098 (0.102) (0.190 - 0.249) All lead tips Typ. All Leads 8-Pin Molded Small Outline Package ...

Page 12

... Life Support Policy Fairchild's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Fairchild Semiconductor Corporation. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support ...