pc87317vul National Semiconductor Corporation, pc87317vul Datasheet - Page 190

pc87317vul

Manufacturer Part Number

pc87317vul

Description

Pc87317vul/pc97317vul Superi/o Plug And Play Compatible With Acpi Compliant Controller/extender

Manufacturer

National Semiconductor Corporation

Datasheet

1.PC87317VUL.pdf

(272 pages)

- Current page: 190 of 272

- Download datasheet (2Mb)

www.national.com

Bit 6 - Reserved

Bit 7 - Automatic Module Configuration (AMCFG)

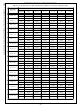

7.19 UART2 WITH IR REGISTER BITMAPS

7

7

Bit 5 of IRCFG4

0: Pin’s direction is input.

1: Pin’s direction is output.

Read/write 0.

When set to 1, this bit enables automatic infrared con-

figuration.

TABLE 7-29. Infrared Receiver Input Selection

(IRSL0_DS)

1. IRCFG4 is in bank 7, offset 07h. It is

2. AUX_IRRX (bit 4 of IRCR2) is described on

6

6

described on page 189.

page 183.

5

5

0

0

1

1

4

4

3

3

1

Transmitted Data

Received Data

2

2

Read Cycles

Write Cycles

Bit 4 of IRCR2

(AUX_IRRX)

1

1

0

0

0

1

0

1

Reset

Required

Reset

Required

Enhanced Serial Port with IR - UART2 (Logical Device 5)

2

Transmitter Data

Selected IRRX

Register (RXD)

Register (TXD)

Receiver Data

IRRX1

IRRX2

IRRX1

Offset 00h

Offset 00h

1

Bank 0,

Bank 0,

190

0

0

7

0

0

0

0

7

7

7

Reserved

Reserved

FEN1 - FIFO Enabled

0

0

6

0

0

0

RXFTH1

6

6

0

6

Reserved

FEN0 - FIFO Enabled

Reserved

0

RXFTH0

5

0

0

0

5

5

0

Non-Extended Modes, Read Cycles

5

0

TXEMP_IE

TXEMP-EV

Extended Mode, Read Cycles

TXFTH1

4

0

0

0

0

4

4

4

Reserved

DMA_IE

DMA_EV

0

TXFTH0

3

0

0

0

0

3

Reserved

3

3

MS_IE

0

MS_EV

2

0

RXFT - RX_FIFO Time-Out

0

Reserved

Write Cycles

0

2

2

2

Extended Mode

LS_EV or TXHLT_EV

LS_IE or TXUR_IE

TXSR

0

1

0

0

IPR1 - Interrupt Priority 1

0

1

1

1

TXLDL_EV

TXLDL_IE

0

IPR0 - Interrupt Priority 0

RXSR

0

1

1

0

0

0

0

Reset

Required

RXHDL_EV

Reset

Required

IPF - Interrupt Pending

Reset

Required

RXHDL_IE

Reset

Required

FIFO_EN

Event Identification

Event Identification

Interrupt Enable

Register (FCR)

Register (IER)

Register (EIR)

Register (EIR)

FIFO Control

Offset 01h

Offset 02h

Offset 02h

Offset 02h

Bank 0,

Bank 0,

Bank 0,

Bank 0,

Related parts for pc87317vul

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Freescale Semiconductor Technical Data

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Self-calibrating 12-bit Plus Sign Serial I/o A/d Converters With Mux And Sample/hold

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Pllatinum Tm Fractional N Rf / Integer N If Dual Low Power Frequency Synthesizer

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Pllatinum? 2.0 Ghz Frequency Synthesizer For Rf Personal Communications

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Pllatinumtm 160 Mhz Frequency Synthesizer For Rf Personal Communications

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Dual N-channel Enhancement Mode Field Effect Transistor

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Video Amplifier System (obsolete)

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Synchronous Step-up DC/DC Converter For White Led Applications

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

CLC420 - High Speed, Voltage Feedback op Amp, Package: Lcc, Pin Nb=20

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Monolithic Triple 4.5 CRT Driver

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Differential Video Amplifier

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

ADC10061 - 10-Bit 600 NS A/D Converter With Input Multiplexer And Sample/Hold, Package: Soic Wide, Pin Nb=20

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

DS36277 - Dominant Mode Multipoint Transceiver, Package: Soic Narrow, Pin Nb=8

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Printer Solenoid Driver

Manufacturer:

National Semiconductor Corporation

Datasheet:

Part Number:

Description:

Quad High Speed Trapezoidal Bus Transceiver

Manufacturer:

National Semiconductor Corporation

Datasheet: