saa5547ps NXP Semiconductors, saa5547ps Datasheet - Page 20

saa5547ps

Manufacturer Part Number

saa5547ps

Description

Saa550x; Saa554x Tv Microcontrollers With Closed Captioning Cc And On-screen Display Osd

Manufacturer

NXP Semiconductors

Datasheet

1.SAA5547PS.pdf

(84 pages)

- Current page: 20 of 84

- Download datasheet (347Kb)

Philips Semiconductors

2000 Feb 23

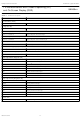

Pulse Width Modulator 6 Control Register (PWM6)

PW6E

PW6V5 to PW6V0

Pulse Width Modulator 7 Control Register (PWM7)

PW7E

PW7V5 to PW7V0

ROM Bank (ROMBK)

STBY

I

ADR6 to ADR0

GC

I

CR2 to CR0

ENSI

STA

STO

2

2

C-bus Slave Address Register (S1ADR)

C-bus Control Register (S1CON)

TV microcontrollers with Closed Captioning (CC)

and On-Screen Display (OSD)

BIT

activate this PWM (logic 1)

pulse width modulator high time

activate this PWM (logic 1)

pulse width modulator high time

Standby mode enabled (logic 1)

I

enable I

clock rate bits; CR<2:0>:

enable I

START flag. When this bit is set in slave mode, the hardware checks the I

and generates a START condition if the bus is free or after the bus becomes free.

If the device operates in master mode it will generate a repeated START

condition.

STOP flag. If this bit is set in a master mode a STOP condition is generated.

A STOP condition detected on the I

in slave mode in order to recover from an error condition. In this case no STOP

condition is generated to the I

SCL lines and switches to the not selected receiver mode. The STOP flag is

cleared by the hardware.

2

C-bus slave address to which the device will respond

000 = 100 kHz bit rate

001 = 3.75 kHz bit rate

010 = 150 kHz bit rate

011 = 200 kHz bit rate

100 = 25 kHz bit rate

101 = 1.875 kHz bit rate

110 = 37.5 kHz bit rate

111 = 50 kHz bit rate

2

2

C-bus general call address (logic 1)

C-bus interface (logic 1)

20

2

C-bus, but the hardware releases the SDA and

FUNCTION

2

C-bus clears this bit. This bit may also be set

Preliminary specification

SAA55xx

2

C-bus

Related parts for saa5547ps

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

NXP Semiconductors designed the LPC2420/2460 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2458 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2468 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2470 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2478 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The XA-S3 device is a member of Philips Semiconductors? XA(eXtended Architecture) family of high performance 16-bitsingle-chip microcontrollers

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP BlueStreak LH75401/LH75411 family consists of two low-cost 16/32-bit System-on-Chip (SoC) devices

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3130/3131 combine an 180 MHz ARM926EJ-S CPU core, high-speed USB2

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3141 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3143 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3152 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3154 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

Standard level N-channel enhancement mode Field-Effect Transistor (FET) in a plastic package using NXP High-Performance Automotive (HPA) TrenchMOS technology

Manufacturer:

NXP Semiconductors

Datasheet: