MC68HC705 MOTOROLA [Motorola, Inc], MC68HC705 Datasheet - Page 140

MC68HC705

Manufacturer Part Number

MC68HC705

Description

HCMOS Microcontroller Unit

Manufacturer

MOTOROLA [Motorola, Inc]

Datasheet

1.MC68HC705.pdf

(222 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68HC705

Manufacturer:

MOTOROLA

Quantity:

9 066

Company:

Part Number:

MC68HC705B16

Manufacturer:

MOT

Quantity:

5 510

Company:

Part Number:

MC68HC705B16

Manufacturer:

OMRON

Quantity:

5 510

Part Number:

MC68HC705B16

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

Company:

Part Number:

MC68HC705B16CFN

Manufacturer:

MOT

Quantity:

5 510

Part Number:

MC68HC705B16CFN

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC68HC705B16NCFN

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC68HC705B5B

Manufacturer:

MOTOROLA

Quantity:

20 000

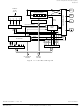

Serial Peripheral Interface (SPI)

11.4 Operation

Technical Data

140

$000C

$000A

$000B

Addr.

SPI Control Register

SPI Status Register

SPI Data Register

Register Name

See page 147.

See page 149.

See page 147.

(SPCR)

(SPDR)

(SPSR)

The master/slave SPI allows full-duplex, synchronous, serial

communication between the microcontroller unit (MCU) and peripheral

devices, including other MCUs. As the 8-bit shift register of a master SPI

transmits each byte to another device, a byte from the receiving device

enters the master SPI shift register. A clock signal from the master SPI

synchronizes data transmission.

Only a master SPI can initiate transmissions. Software begins the

transmission from a master SPI by writing to the SPI data register

(SPDR). The SPDR does not buffer data being transmitted from the SPI.

Data written to the SPDR goes directly into the shift register and begins

the transmission immediately under the control of the serial clock. The

transmission ends after eight cycles of the serial clock when the SPI flag

(SPIF) becomes set. At the same time that SPIF becomes set, the data

shifted into the master SPI from the receiving device transfers to the

SPDR. The SPDR buffers data being received by the SPI. Before the

master SPI sends the next byte, software must clear the SPIF bit by

reading the SPSR and then accessing the SPDR.

Figure 11-2. SPI I/O Register Summary

Reset:

Reset:

Reset:

Read:

Read:

Read:

Write:

Write:

Write:

Serial Peripheral Interface (SPI)

SPIE

SPIF

Bit 7

Bit 7

0

0

= Unimplemented

WCOL

SPE

Bit 6

6

0

0

Bit 5

5

U = Unaffected

MODF

MSTR

Unaffected by reset

Bit 4

4

0

0

CPOL

Bit 3

U

3

MC68HC705C8A — Rev. 2.0

CPHA

BIt 2

U

2

SPR1

Bit 1

U

1

MOTOROLA

SPR0

Bit 0

Bit 0

U