XC17128DDD8M Xilinx, XC17128DDD8M Datasheet

XC17128DDD8M

Available stocks

Related parts for XC17128DDD8M

XC17128DDD8M Summary of contents

Page 1

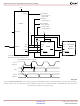

... Figure 1: Simplified Block Diagram (does not show programming circuit) © 2000 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. ...

Page 2

... High RESET, but the preferred option is active Low RESET, because it can be driven by the FPGAs INIT pin. The polarity of this pin is controlled in the programmer inter- face. This input pin is easily inverted using the Xilinx HW-130 programmer software. Third-party programmers have different methods to invert this pin. ...

Page 3

... FPGA mode pins. In Master Serial mode, the FPGA automatically loads the configuration pro- gram from an external memory. The Xilinx PROMs have been designed for compatibility with the Master Serial mode. Upon power-up or reconfiguration, an FPGA enters the Master Serial mode whenever all three of the FPGA mode-select pins are Low (M0=0, M1=0, M2=0) ...

Page 4

... FPGAs with Different configurations OPTIONAL Slave FPGAs with Identical Configurations V CC 3.3V 4. DATA DIN CLK CE INIT OE/RESET cycle before the FPGA I/Os become active. www.xilinx.com 1-800-255-7778 DATA PROM CLK CEO CE OE/RESET DS070 (v2.1) June 1, 2000 Product Specification R Cascaded Serial Memory DS027_02_052200 ...

Page 5

... QPRO Family of XC1700D QML Configuration PROMs Programming The devices can be programmed on programmers supplied by Xilinx or qualified third-party vendors. The user must ensure that the appropriate programming algorithm and the latest version of the programmer software are used. The wrong choice can permanently damage the device. ...

Page 6

... C must be connected Description = –4 mA) Military mA) OL XC17128D, XC17256D XC1736D, XC1765D = GND 1.0 MHz) sample tested IN = GND 1.0 MHz) sample tested IN www.xilinx.com 1-800-255-7778 Units –0.5 to +7.0 –0.5 to +12.5 –0 0.5 CC –0 0.5 CC –65 to +150 +260 Min Max Units Military 4 ...

Page 7

... Float delays are measured with loads. Transition is measured at ±200mV from steady state active levels. DS070 (v2.1) June 1, 2000 Product Specification QPRO Family of XC1700D QML Configuration PROMs (1,2) T SCE CAC Description (3) (3,4) = 0.0V and V = 3.0V www.xilinx.com 1-800-255-7778 T SCE T HCE T HOE T CYC DS027_03_021500 XC1736D XC17128D XC1765D XC17256D Min Max Min ...

Page 8

... Guaranteed by design, not tested. 4. Float delays are measured with loads. Transition is measured at ±200mV from steady state active levels CDF Last Bit T OCK T OCE Description (3,4) (3) = 0.0V and V = 3.0V www.xilinx.com 1-800-255-7778 (1,2) First Bit T OOE T OCE DS027_04_021500 XC1736D XC17128D XC1765D XC17256D Min Max Min Max - ...

Page 9

... R Ordering Information Device Number XC1736D XC1765D XC17128D XC17256D Valid Ordering Combinations XC17128DDD8M XC17256DDD8M 5962-9561701MPA Marking Information Due to the small size of the PROM package, the complete ordering part number cannot be marked on the package. Device Number XC1736D XC1765D XC17128D XC17256D Revision History The following table shows the revision history for this document ...

Page 10

... QPRO Family of XC1700D QML Configuration PROMs 10 www.xilinx.com 1-800-255-7778 R DS070 (v2.1) June 1, 2000 Product Specification ...