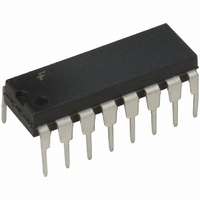

MM74C221N Fairchild Semiconductor, MM74C221N Datasheet

MM74C221N

Specifications of MM74C221N

74C221N

Available stocks

Related parts for MM74C221N

MM74C221N Summary of contents

Page 1

... Plastic Dual-in-Line Package (PDIP), JEDEC MS-001, 0.300” Wide Connection Diagrams Timing Component Pin Assignments for DIP Top View © 1999 Fairchild Semiconductor Corporation Pulse stability will be limited by the accuracy of external timing components. The pulse width is approximately defined by the relationship t ther information and applications, see AN-138. ...

Page 2

Absolute Maximum Ratings Voltage at Any Pin 0. Operating Temperature Range Storage Temperature Range Power Dissipation Dual-In-Line Small Outline Operating V Range CC DC Electrical Characteristics Max/min limits apply across temperature range, unless otherwise noted Symbol Parameter CMOS ...

Page 3

AC Electrical Characteristics pF, unless otherwise noted A L Symbol Parameter t Propagation Delay from Trigger Input ( Output Propagation Delay from Clear pd CL Input (CL) ...

Page 4

Typical Performance Characteristics 0% Point pulse width 5V 10V 15V,T 9 Percentage of units within 4 5V,90% of units CC ...

Page 5

Typical Performance Characteristics Switching Time Waveforms (Continued) 5 www.fairchildsemi.com ...

Page 6

Physical Dimensions inches (millimeters) unless otherwise noted 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL ...