CYIL1SE0300-EVAL Cypress Semiconductor Corp, CYIL1SE0300-EVAL Datasheet - Page 22

CYIL1SE0300-EVAL

Manufacturer Part Number

CYIL1SE0300-EVAL

Description

BOARD EVAL IMAGE SENSOR LUPA-300

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CYIL1SE0300-EVAL.pdf

(31 pages)

Specifications of CYIL1SE0300-EVAL

Sensor Type

CMOS Imaging, Color (RGB)

Sensing Range

VGA

Interface

SPI

Sensitivity

250 fps

Voltage - Supply

2.5 V ~ 3.3 V

Embedded

No

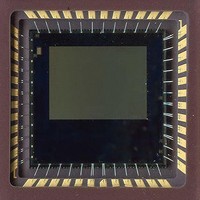

Utilized Ic / Part

LUPA-300

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Startup Timing

On startup, VDDD should rise together with or before the other

supplies. The rise of VDDD should be limited to 1V/100 μs to

avoid activation of the on chip ESD protection circuitry.

During the rise of VDDD an on chip POR_N signal is generated

that resets the SPI registers to its default setting. After VDDD is

stable the SPI settings can be uploaded to configure the sensor

for future readout and light integration. When powering on the

VDDD supply, the RESET_N pin should be kept low to reset the

Sequencer Reset Timing

By bringing RESET_N low for at least 50 ns, the on chip

sequencer is reset to its initial state. The internal clock division is

restarted. The second rising edge of CLK after the rising edge of

Document Number: 001-00371 Rev. *F

System clock

VDDD power

RESET_N

Core clock

SPI upload

(external)

(internal)

POR_N

(internal)

Core clock

RESET_N

(external)

(internal)

(internal)

supply

(internal)

System

Sync_Y

Clock_Y

clock

INT_TIME1

POWER ON

INVALID

Normal operation

FOT

Min 500ns

SPI upload

Reset

Figure 24. Sequencer Reset Timing

Readout

Figure 23. Startup Timing

Min 50 ns

INVALID

on chip sequencer and addressing logic. The RESET_N pin

must remain low until all initial SPI settings are uploaded.

RESET_N pin must remain low for at least 500 ns after ALL

supplies are stable. The rising edge of RESET_N starts the on

chip clock division. The second rising edge of CLK after the rising

edge of RESET_N, triggers the rising edge of the core clock.

Some SPI settings can be uploaded after the core clock has

started.

RESET_N the internal clock is restarted. The SPI settings are

not affected by RESET_N. If needed the SPI settings can be

changed during a low level of RESET_N.

VDDD STABLE

INVALID

Integration

LINE_VALIDs

Dummy

SPI upload if required

CYIL1SM0300AA

FOT

Normal operation

Page 22 of 31

[+] Feedback