ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 19

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

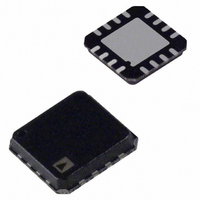

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

Synchronous Single Device Point-to-Point Topology

A single device is wired in the point-to-point configuration as

shown in Figure 15. The standard use of this configuration is

with no delay devices. It is possible to use this topology with

fixed delay devices as well, such as if line noise reduction after a

sync pulse transmission is desired.

SYNCHRONOUS COMMUNICATION MODE—DUAL

DEVICE

The ADXL180 can be used in a dual device synchronous

communication mode. This mode allows a maximum of two

Figure 15. Single Device—Synchronous Communication

MODULE

CENTER

V

BP

V

DEVICE 1

BN

V

NC

BN

V

NC

BC

Rev. A | Page 19 of 60

ADXL180 devices to share a single pair of wires from the

control module for power and communications. This is

accomplished using time division multiplexing where each

device transmits its data during a known time slot. The time

slot used by each device is determined by the delay time from

detection of a synchronization pulse to the beginning of data

transmission. The data transmission delay time is selectable in

the configuration registers. The following discussion uses the

convention that the first time slot is named Time Slot A and the

second time slot is named Time Slot B (see Figure 16). The two

ADXL180 devices can be wired in either a parallel or series

mode as described in the following sections. If a synchronization

pulse is not detected, no data is sent. This is true for all initiali-

zation phases and normal run-time operation. Note that the

minimum synchronization pulse period is

t

SPD

+ t

DLY

+ t

M

+ t

B

ADXL180