EVAL-ADAU1761Z Analog Devices Inc, EVAL-ADAU1761Z Datasheet - Page 45

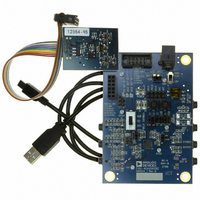

EVAL-ADAU1761Z

Manufacturer Part Number

EVAL-ADAU1761Z

Description

Eval Board For ADAU1761

Manufacturer

Analog Devices Inc

Series

SigmaDSP®r

Specifications of EVAL-ADAU1761Z

Main Purpose

Audio, CODEC

Embedded

Yes, DSP

Utilized Ic / Part

ADAU1761

Primary Attributes

Stereo, 24-Bit, 8 ~ 96 kHz Sampling Rate, GUI Tool

Secondary Attributes

I²C and GPIO Interfaces, 2 Differential and 1 Stereo Single-Ended Analog Inputs and Outputs

Silicon Manufacturer

Analog Devices

Core Architecture

SigmaDSP

Silicon Core Number

ADAU1761

Silicon Family Name

SigmaDSP

Application Sub Type

Audio

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EVAL-ADAU1761Z

Manufacturer:

Analog Devices Inc

Quantity:

135

DSP CORE

SIGNAL PROCESSING

The ADAU1761 is designed to provide all audio signal processing

functions commonly used in stereo or mono low power record

and playback systems. The signal processing flow is designed

using the SigmaStudio software, which allows graphical entry

and real-time control of all signal processing functions.

Many of the signal processing functions are coded using full,

56-bit, double-precision arithmetic data. The input and output

word lengths of the DSP core are 24 bits. Four extra headroom

bits are used in the processor to allow internal gains of up to

24 dB without clipping. Additional gains can be achieved by

initially scaling down the input signal in the DSP signal flow.

ARCHITECTURE

The DSP core consists of a simple 28-/56-bit multiply-accumulate

(MAC) unit with two sources: a data source and a coefficient

source. The data source can come from the data RAM, a ROM

table of commonly used constant values, or the audio inputs to

the core. The coefficient source can come from the parameter

RAM or from a ROM table of commonly used constant values.

The two sources are multiplied in a 28-bit fixed-point multiplier

and then the signal is input to the 56-bit adder; the result is usually

stored in one of three 56-bit accumulator registers. The accumu-

lators can be output from the core (in 28-bit format) or can

optionally be written back into the data or parameter RAMs.

ROM CONSTANTS,

AUDIO INPUTS)

DATA SOURCE

(DATA RAM,

(ACCUMULATORS (3), dB CONVERSION,

28

BIT OPERATORS, BIT SHIFTER, ...)

Figure 67. Simplified DSP Core Architecture

56

DATA OPERATIONS

TRUNCATOR

OUTPUTS

56

56

28

COEFFICIENT SOURCE

(PARAMETER RAM,

ROM CONSTANTS)

28

TRUNCATOR

28

56

Rev. C | Page 45 of 92

PROGRAM COUNTER

The execution of instructions in the core is governed by a program

counter, which sequentially steps through the addresses of the

program RAM. The program counter starts every time that a

new audio frame is clocked into the core. SigmaStudio inserts

a jump-to-start command at the end of every program. The

program counter increments sequentially until it reaches this

command and then jumps to the program start address and

waits for the next audio frame to clock into the core.

FEATURES

The SigmaDSP core was designed specifically for audio processing

and therefore includes several features intended for maximizing

efficiency. These include hardware decibel conversion and audio-

specific ROM constants.

STARTUP

Before the DSPRUN bit is set or any settings are written to the

parameter RAM, the DSP core must be enabled by setting the

DSPEN bit in Register R61 (Address 0x40F5).

The following steps should be performed every time that a new

program is loaded to the SigmaDSP core, or any time that the

DSPRUN bit is disabled and reenabled.

1.

2.

3.

4.

5.

Changing any register setting or RAM can cause pops and

clicks on the analog outputs. To avoid these pops and clicks,

mute the appropriate outputs using Register R29 to Register R32

(Address 0x4023 to Address 0x4026). Unmute the analog out-

puts after the startup procedure is completed.

Set the DSPSR[3:0] bits in Register R57 (Address 0x40EB)

to 1111 (none).

Set the DSPRUN bit in Register R62 (Address 0x40F6) to 0.

Download the rest of the registers, the program RAM, and

the parameter RAM.

Set the DSPRUN bit in Register R62 to 1.

Set the DSPSR[3:0] bits in Register R57 to the operational

setting (default value is 0001).

ADAU1761