EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 179

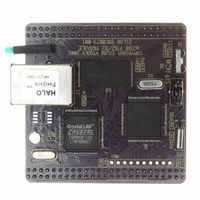

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 179 of 269

- Download datasheet (4Mb)

Figure 41.ZDI Single-Byte Data Write Timing

PS015308-0404

ZDA

ZCL

ZDI Write Operations

ZDI Address

lsb of

can be repeated. Repeated Read or Write operations can occur without requiring a resend

of the ZDI command. To initiate a new ZDI command, a START signal must follow.

Figure 40 illustrates the timing for address Writes to ZDI registers.

Figure 40.ZDI Address Write Timing

ZDI Single-Byte Write

For single-byte Write operations, the address and Write control bit are first written to the

ZDI block. Following the single-bit byte separator, the data is shifted into the ZDI block

on the next 8 rising edges of ZCL. The master terminates activity after 8 clock

cycles.Figure 41 illustrates the timing for ZDI single-byte Write operations.

A0

ZDA

ZCL

7

Write

START

8

Signal

Byte Separator

S

Single-Bit

0/1

9

msb

A6

of DATA

1

msb

D7

1

A5

2

D6

P R E L I M I N A R Y

2

A4

3

D5

3

ZDI Address Byte

A3

ZDI Data Byte

D4

4

4

A2

D3

5

5

D2

A1

6

6

D1

A0

7

lsb

7

Product Specification

0 = WRITE

1 = READ

of DATA

ZiLOG Debug Interface

eZ80F92/eZ80F93

D0

R/W

lsb

8

8

Byte Separator

START Signal

START Signal

End of Data

or New ZDI

or new ZDI

Single-Bit

0/1

1

9

9

167

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: