EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 53

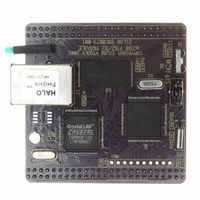

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 53 of 269

- Download datasheet (4Mb)

General-Purpose Input/Output

Table 6. GPIO Mode Selection

PS015308-0404

GPIO

Mode

1

2

GPIO Overview

GPIO Operation

Px_ALT2

Bits7:0

0

0

0

0

The eZ80F92 device features 24 General-Purpose Input/Output (GPIO) pins. The GPIO

pins are assembled as three 8-bit ports— Port B, Port C, and Port D. All port signals can

be configured for use as either inputs or outputs. In addition, all of the port pins can be

used as vectored interrupt sources for the CPU.

The GPIO operation is the same for all 3 GPIO ports (Ports B, C, and D). Each port fea-

tures eight GPIO port pins. The operating mode for each pin is controlled by four bits that

are divided between four 8-bit registers. These GPIO mode control registers are:

•

•

•

•

where x can be B, C, or D representing any of the three GPIO ports B, C, or D. The mode

for each pin is controlled by setting each register bit pertinent to the pin to be configured.

For example, the operating mode for Port B Pin 7 (PB7), is set by the values contained in

PB_DR[7], PB_DDR[7], PB_ALT1[7], and PB_ALT2[7].

The combination of the GPIO control register bits allows individual configuration of each

port pin for nine modes. In all modes, reading of the Port x Data register returns the sam-

pled state, or level, of the signal on the corresponding pin. GPIO Mode Selection indicates

the function of each port signal based upon these four register bits. After a RESET event,

all GPIO port pins are configured as standard digital inputs, with interrupts disabled.

Port x Data Register (Px_DR)

Port x Data Direction Register (Px_DDR)

Port x Alternate Register 1 (Px_ALT1)

Port x Alternate Register 2 (Px_ALT2)

Px_ALT1

Bits7:0

0

0

0

0

Px_DDR

Bits7:0

0

0

1

1

Bits7:0 Port Mode

Px_DR

P R E L I M I N A R Y

0

1

0

1

Output

Output

Input from pin

Input from pin

General-Purpose Input/Output

Product Specification

eZ80F92/eZ80F93

Output

0

1

High impedance

High impedance

41

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: