SAA7146AH NXP Semiconductors, SAA7146AH Datasheet - Page 70

SAA7146AH

Manufacturer Part Number

SAA7146AH

Description

Manufacturer

NXP Semiconductors

Datasheet

1.SAA7146AH.pdf

(139 pages)

Specifications of SAA7146AH

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SAA7146AH

Manufacturer:

NXP

Quantity:

5 510

Company:

Part Number:

SAA7146AH

Manufacturer:

PHILIPS

Quantity:

875

Part Number:

SAA7146AH

Manufacturer:

PHILIPS

Quantity:

20 000

Part Number:

SAA7146AH/V3

Manufacturer:

PHILIPS/飞利浦

Quantity:

20 000

Company:

Part Number:

SAA7146AH/V4

Manufacturer:

NXP

Quantity:

12 000

Part Number:

SAA7146AH/V4

Manufacturer:

NXP/恩智浦

Quantity:

20 000

Company:

Part Number:

SAA7146AH/V4,557

Manufacturer:

NXP Semiconductors

Quantity:

10 000

Part Number:

SAA7146AHZ

Manufacturer:

PHILIPS/飞利浦

Quantity:

20 000

Philips Semiconductors

7.9.3

In the phase correct Horizontal Phase Scaling (HPS) the

pixels are calculated for the geometrically correct,

orthogonal output pattern, down to

pattern. A horizontal zooming feature is also supported.

The maximum zooming factor is at least 2, even more

dependent on input pattern and prescaling settings.

The phase scaling consists of a filter and an arithmetic

structure which is able to generate a phase correct new

pixel value almost without phase or amplitude artefacts.

The required sample phase information is generated by a

sample phase calculator, with an accuracy of

pixel distance. The up/downscaling with this circuitry is

controlled by the scaler register parameters XSCI and XP.

As the fine scaling is restricted to downscales (

fine scalers input pixel count), XSCI is also a function of

the prescaling parameter XPSC.

With N

N

defined to:

XSCI = INT [(N

The maximum value of XSCI = 4095. Zooming is

performed for XSCI values less than 1024. The number of

disqualified clock cycles between consecutive pixel

qualifiers (at the fine scalers input) defines the maximum

possible zoom factor. Consequently, zooming may also be

a function of XPSC. It should be noted that if the zooming

factor is greater than 2, some artefacts may occur at the

end of the zoomed line.

7.9.4

The scaled YUV output data is converted after

interpolation into RGB data according to CCIR 601

recommendations. The CSM is bypassed in all YUV

formats or monochrome modes.

The matrix equations considering the digital quantization

are:

A dither algorithm is implemented for error diffusion. ROM

tables are implemented at the matrix output to provide

anti-gamma correction of the RGB data. A curve for a

gamma of 1.4 is implemented. The tables can be used to

compensate gamma correction for linear data

representation of RGB output data.

2004 Aug 25

OP

R = Y + 1.375V

G = Y

B = Y + 1.734375U.

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

= Number of desired Output Pixels/line, XSCI is

IP

H

= Number of Input Pixel/line (at DD1 input) and

C

-

0.703125V

ORIZONTAL PHASE SCALING

OLOUR

CORRECTION

IP

/N

S

OP

PACE

)

0.34375U

M

1024/(XPSC + 1)]

ATRIX

(CSM),

1

4

of the prescaled

DITHER AND

1

64

1

of the

4

of the

70

The ‘Chroma Signal Key’ generates an alpha signal used

in several RGB formats. Therefore, the processed UV data

amplitudes are compared with thresholds. A logic 1 is

generated, if the amplitude is within the specified

amplitude range. Otherwise a logic 0 is generated. Keying

can be switched off by setting the lower limit higher than

the upper limit.

7.10

7.10.1

The BRS is the second scaler in the SAA7146A. The BRS

is supposed to support different encoder applications while

the HPS is processing video data. The BRS does not

support clipping.

The mainstream application of the BRS is to read data via

PCI, e.g. a QCIF-formatted video data to proceed with

horizontal and vertical upscaling to CIF-format and place it

at the encoder’s disposal (normal playback mode).

To support CCIR encoder and square pixel encoder, an

active video window as input for the BRS can be defined.

It will prevent black pixels being displayed at the end of the

line or at the bottom of the field.

The BRS supports only the YUV 4 : 2 : 2 video data format

(see Section 7.11.2). The used DD1 I/O data format is

8-bit. The BRS uses video DMA Channel 3 (FIFO 3) which

is only available, if the HPS is not in planar mode or writes

back clip information.

Vertical upscaling is supported by means of repeated

reading of the same line via PCI. Vertical downscaling is

achieved by line dropping.

Horizontal downscaling is performed by an accumulating

FIR filter. The downscaling is available for the inbound

mode and the upscaling is available for the outbound

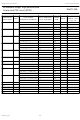

mode (see Figs 22 and 23).

If the data is sent from DD1 to PCI, the processing window

for the BRS scaling unit is defined in the acquisition control

(see Section 7.8.7).

Vertical ratios: 4, 2, 1,

Horizontal ratios: 8, 4, 2, 1,

BRS_H.

Binary Ratio Scaler (BRS)

G

ENERAL DESCRIPTION

1

2

and

1

2

1

,

4

1

; select with BRS_V

4

and

Product specification

SAA7146A

1

8

; select with