saa6703ah NXP Semiconductors, saa6703ah Datasheet

saa6703ah

Available stocks

Related parts for saa6703ah

saa6703ah Summary of contents

Page 1

... DATA SHEET SAA6703AH XGA analog input flat panel controller Product specification INTEGRATED CIRCUITS 2004 Apr 01 ...

Page 2

... TIMING CHARACTERISTICS 13 APPLICATION INFORMATION 14 PACKAGE OUTLINE 15 SOLDERING 15.1 Introduction to soldering surface mount packages 15.2 Reflow soldering 15.3 Wave soldering 15.4 Manual soldering 15.5 Suitability of surface mount IC packages for wave and reflow soldering methods 16 DATA SHEET STATUS 17 DEFINITIONS 18 DISCLAIMERS 19 PURCHASE OF PHILIPS I 2 Product specification SAA6703AH 2 C COMPONENTS ...

Page 3

... Event driven interrupt generation for easy interfacing with microcontroller software. 2 GENERAL DESCRIPTION The SAA6703AH is a single input single-chip Thin Film Transistor (TFT) display controller IC with analog VGA standard input capabilities. Additionally, the SAA6703AH includes a wide range of functions for processing and the measurement of incoming RGB data according to the requirements of an XGA TFT display ...

Page 4

... TYPE NUMBER NAME SAA6703AH QFP160 2004 Apr 01 CONDITIONS DDD(IC9) , DDA( DDA(ADC)(R) DDA(ADC)(G) , DD(PLL)(P) DDA(PLL)(S) DDD(EP10) note 1 PACKAGE DESCRIPTION plastic quad flat package; 160 leads (lead length 1.6 mm); body 28 28 3.4 mm; high stand-off height 4 Product specification SAA6703AH MIN. TYP. MAX. UNIT 2.3 2.5 2.7 V 2.3 2.5 2.7 V 2.3 2.5 2.7 V 2.7 3.0 3.3 V 3.0 3.3 3 ...

Page 5

... I C-BUS JTAG panel clock INTERFACE INTERFACE sample clock configuration test control data signals syncs MODE DETECTION SAA6703AH AUTO- ADJUSTMENT RGB data 3 8-bit DOWN- DECOUPLING UPSCALER SCALER FIFO COLOUR OSD LOOK-UP DITHERING RGB data RGB data TABLE 3 10-bit ...

Page 6

... V) not connected not connected internal digital core supply ground 2 not connected connect with a pull-up resistor of 51 internal digital core supply voltage 3 (2.5 V) internal digital core supply ground 3 not connected 6 Product specification SAA6703AH DESCRIPTION to V (3.3 V) DDE ...

Page 7

... B bit 5 panel data port B bit 6 panel data port B bit 7 external digital pad supply ground 4 external digital pad supply voltage 4 (3.3 V) panel data port C bit 0 7 Product specification SAA6703AH DESCRIPTION (3 DDE (3 DDE 2 C-bus slave address input, latched ...

Page 8

... V) panel data port F bit 0 panel data port F bit 1 panel data port F bit 2 panel data port F bit 3 panel data port F bit 4 panel data port F bit 5 panel data port F bit 6 panel data port F bit 7 8 Product specification SAA6703AH DESCRIPTION ...

Page 9

... Product specification SAA6703AH DESCRIPTION 2 C-bus slave address input, latched ...

Page 10

... Table 1 Pin type description TYPE A analog input I digital input O digital output I/O digital input or output 2004 Apr 01 external analog pad supply ground external analog pad supply voltage (3.3 V) analog test pad (should be connected to analog ground for application) DESCRIPTION 10 Product specification SAA6703AH DESCRIPTION ...

Page 11

... V SSD(IC2) 35 n.c. 36 RESERVED1 37 V DDD(IC3 SSD(IC3) 39 n.c. 40 2004 Apr 01 SAA6703AH Fig.2 Pin configuration. 11 Product specification SAA6703AH 120 PF6 119 PF5 118 PF4 117 PF3 116 PF2 115 PF1 114 PF0 V DDD(EP7) 113 V SSD(EP7) 112 111 PE7 110 ...

Page 12

... C-bus subaddresses 11 7.1.2.2 The SAA6703AH only operates as a slave and the clock pin SCL is exclusively input. Data is transmitted and received at I/O pin SDA. The SDA is an open-drain stage with an external pull-up resistor. When a logic 0 is applied, the bus is pulled to LOW-level by the output buffer. When a logic 1 is applied, the output buffer switches to 3-state and the pull-up resistor pulls the bus up to HIGH-level ...

Page 13

... SCL is at HIGH-level (see Fig.4). 2 7.1.2.3 I C-bus device address 2 Bits A0 and A1 of the I C-bus device address are externally selected by two input pins CSG2/A0 and CSG4/A1. The device address (byte) of the SAA6703AH is shown in Table 4. 2 Table 4 I C-bus device address byte MSB DEVICE ADDRESS BITS ...

Page 14

... I C-bus. Any programmed value can be read back. 2 7.1 BUS REGISTER LISTING The global registers are listed in Table 6. The page-mapped registers are listed for each register page in Tables 7 to 17. 14 Product specification SAA6703AH ...

Page 15

Acrobat reader. white to force landscape pages to be ... Table 6 Global configuration registers REGISTER ADR R/W RESET Global control: FAH to FFH ...

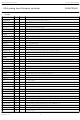

Page 16

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET SYNC_DIS 19H W 000 0000 PLL programming: 20H to 29H ...

Page 17

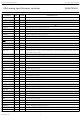

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET ADC_G_CON 04H W 00H adc_green_contrast[7:0] ADC_B_BRI 05H W 00H adc_blue_brightness[7:0] ...

Page 18

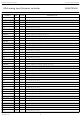

Acrobat reader. white to force landscape pages to be ... Table 10 Auto-adjustment configuration registers (page 3); note 1 REGISTER ADR R/W RESET Auto-adjustment: ...

Page 19

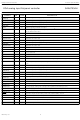

Acrobat reader. white to force landscape pages to be ... Note don’t care. Table 11 Input interface configuration registers (page 4) ...

Page 20

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET PG_HINC2 18H W FFH h_colour_inc2[7:0] PG_VSTEP1 19H W 14H v_step1[7:0] ...

Page 21

Acrobat reader. white to force landscape pages to be ... Table 14 Scaler configuration registers (page 7); note 1 REGISTER ADR R/W RESET Upscaler: ...

Page 22

Acrobat reader. white to force landscape pages to be ... Table 15 Definition of OSD configuration registers (pages 8 and 9); note 1 REGISTER ...

Page 23

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_CC_HI 16H single_ char_def OSDT_CC_LO 17H W ...

Page 24

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSD : 40H 4CH POINTER TO OSDP_CTRL0 40H W 0000 ...

Page 25

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_FGC4B 0EH W 00H osd_text_foreground_colour4_blue[7:0] OSDT_FGC5R 0FH W 00H osd_text_foreground_colour5_red[7:0] ...

Page 26

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_BGC7G 2EH W FFH osd_text_background_colour7_green[7:0] OSDT_BGC7B 2FH W FFH osd_text_background_colour7_blue_7[7:0] ...

Page 27

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_P2C2R 4EH W 00H osd_palette2_colour2_red[7:0] OSDT_P2C2G 4FH W 80H osd_palette2_colour2_green[7:0] ...

Page 28

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_P5C0B 6EH W 00H osd_palette5_colour0_blue[7:0] OSDT_P5C1R 6FH W 7FH osd_palette5_colour1_red[7:0] ...

Page 29

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDT_P7C3G 8EH W 00H osd_palette7_colour3_green[7:0] OSDT_P7C3B 8FH W 00H osd_palette7_colour3_blue[7:0] ...

Page 30

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDB_C8B ADH W 40H osd_bitmap_colour8_blue[7:0] OSDB_C9R AEH W 80H osd_bitmap_colour9_red[7:0] ...

Page 31

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OSDP_C3R CCH W 00H osd_pointer_colour3_red[7:0] OSDP_C3G CDH W 00H osd_pointer_colour3_green[7:0] ...

Page 32

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OI_PSY_LO 08H W 07H picture_start_y[7:0] OI_ASX_HI 09H W 000 OI_ASX_LO ...

Page 33

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OI_PED 28H W 0000 0000 pin_drv_pe[2:0] OI_PFD 29H W 0000 ...

Page 34

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OI_G1ASX_HI 51H W 000 OI_G1ASX_LO 52H W 03H point1_x[7:0] OI_G1ASY_HI ...

Page 35

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OI_G3SX_HI 81H W 000 OI_G3SX_LO 82H W 00H point1_x[7:0] OI_G3SY_HI ...

Page 36

Acrobat reader. white to force landscape pages to be ... REGISTER ADR R/W RESET OI_PWMD F6H W 000 pin_drv_pwm[2:0] OI_WC F6H R 00H wait_count[7:0] ...

Page 37

... LINE-LOCKED 0 PLL PHASE SHIFT 1 configuration signals configuration signals bclk_in_en PANEL CLOCK 0 PLL 1 Fig.5 Clock distribution. 37 Product specification SAA6703AH Clock management ADC sample clock VCLK (I/O) vclk_in_en 0 front-end clock 1 frontend_bclk back-end clock 0 system clock 4 1 clk_div4 2 0 ...

Page 38

... I DESCRIPTION See Table 21 for configuration clock switching options. Table 21 Configuration clock switching modes cfgclk_select 38 Product specification SAA6703AH FRONT-END vclk_in_en CLOCK X back-end clock 1 VCLK ...

Page 39

... PLL PROGRAMMING The SAA6703AH contains two PLLs: Line-locked PLL generating the sample clock from the hsync signal (see Fig.6) PLL running on the system clock generating the panel clock (see Fig.7). The PLL programming registers are mapped to register page 0 ...

Page 40

... Figure 9 shows the composite sync modes that can be used. The maximum number of equalizing pulses (csync-3 and csync-4) may not exceed 30. Table 22 Composite sync decoder input selection sog_en Product specification SAA6703AH pll_m_div [ 1:0 ] PLL m-DIVIDER 2 clock MHC214 CSYNC SOG HSYNC ...

Page 41

... DETECTION VSYNC 2004 Apr HSYNC hs_regen_in_en HS_CS COMPOSITE SYNC VS_CS DECODER ACTIVITY DETECTION 0 VSYNC ACTIVITY 1 DETECTION Fig.8 Synchronization pulse distribution. 41 Product specification SAA6703AH mdd_cs_sog_en HSYNC mdd_hs_regen_on HSYNC iif_cs_sog_en iif_hs_regen_on HSYNC REGENERATION HS_REGEN HSYNC 0 1 iif_cs_sog_en ...

Page 42

... Tables 25 and 26). HS_REGEN Table 25 Mode detection sync selection; note 1 mdd_cs_ sog_en - PLL LOCKED Note don’t care. VS_PLL VSYNC VS_CS 42 Product specification SAA6703AH S ELECTION OF SYNCS FOR MODE DETECTION AND INPUT INTERFACE mdd_hs_ HS_MDD regen_on 0 X HSYNC 1 0 HS_CS 1 1 ...

Page 43

... II_HJIT, indicating that the other clock edge should be used to sample the hsync and vsync signal. 43 Product specification SAA6703AH SUBMODULE DESCRIPTION mode detection change of input video mode detected auto-adjustment auto-adjustment fi ...

Page 44

... LOW active. The gain correction pulse generation is enabled by setting gainc_en. During gain correction the ADC inputs are connected to a reference voltage and by gain adjustment the output is matched to adc_red_contrast, adc_green_contrast and adc_blue_contrast. clamp_off_delay clamp_on_delay gainc_off_delay Fig.10 Gain adjustment and clamp pulse generation. 44 Product specification SAA6703AH MHC218 ...

Page 45

... SYNC-ON-GREEN CLAMP C1 ADC AGC C1 CLAMP C1 ADC AGC C1 Fig.11 Analog video input block diagram. 45 Product specification SAA6703AH DIGITAL PART clamp pulse ADC clock gain pulse brightness setting (8-bit) blue channel output (8-bit) contrast setting (8-bit) sync output SOG enable brightness ...

Page 46

... Fig.13). The length defines width and height of the sampled frame. The vertical sample offset and length are given in lines and the horizontal offset and length are measured in pixels. 46 Product specification SAA6703AH ...

Page 47

... It generates a picture of the size defined by in_h_length and in_v_length with additional blanking. The total line length and number of lines are defined by h_length_total and v_length_total. The input interface sample offset is without effect when using the picture generator. 47 Product specification SAA6703AH h_length MHB253 4 5 ...

Page 48

... The interrupt is level-based, so every frame after a certain number of occurrences until the next vsync the interrupt state is set to logic 1. The jitter detection does not work correctly without a vsync signal. h_step1 h_step2 h_colour_dec h_colour_inc column position 48 Product specification SAA6703AH wrap around MHC221 ...

Page 49

... RGB mode detection and auto-adjustment The SAA6703AH can be used to build up auto-scan systems using an external microcontroller. Therefore, information about the input resolution and timing are measured by the SAA6703AH that can be read out via the 2 I C-bus. Provided information can be divided into mode detection ...

Page 50

... Parameter ref_colour_0 is used to determine the start of the active video area. If the sample value of at least one of the three colour components is above this value the pixel is treated as upper left corner of active video. 50 Product specification SAA6703AH A - UTO ADJUSTMENT FUNCTION 00 ...

Page 51

... Active area: shaded. Fig.15 Enhanced mode. ref_col_1 handbook, halfpage start ref_colour_0 ref_colour_0 ref_colour_1 ref_colour_1 eval_col_0 Active area: shaded. Fig.16 Non-enhanced mode. 51 Product specification SAA6703AH eval_row_0 eval_row_1 eval_col_1 MHC222 eval_row_0 ref_row_1 eval_row_1 eval_col_1 MHC223 ...

Page 52

... Apr 01 DESCRIPTION 52 Product specification SAA6703AH ...

Page 53

... Apr 01 DESCRIPTION 53 Product specification SAA6703AH ...

Page 54

... Apr 01 To simplify the measurements, the values can be taken as a single snapshot representing the momentary value of the pixel at the reference position or they can be build up over several frames, which is activated by programming the number of frames to bits aa_cycles. DESCRIPTION 54 Product specification SAA6703AH ...

Page 55

... XGA analog input flat panel controller 7.10.3.4 Phase distortion measurement To help adjusting the phase for the ADCs, the SAA6703AH has a built-in phase distortion measurement which is calculating a 30-bit indicator value of a defined area of the video signal (see Table 35). The area for phase distortion measurements may contain active video or blanking ...

Page 56

... FIFO level exceeds the threshold level, given by fifo_threshold in units of 8 pixels. 7.12 Scaling The SAA6703AH features separate scaling engines for upscaling and downscaling, for both horizontal and vertical processing. Two separate scaling units are implemented to perform upscaling and downscaling. 7.12.1 ...

Page 57

... XGA analog input flat panel controller 7.12.3 H ORIZONTAL FLIPPING The SAA6703AH provides the possibility to flip horizontally the incoming picture. As flipping needs a line memory, both the downscaler and the upscaler have a flip programming register. When using the downscaler flip mode (flip_h = 1), no vertical downscaling can be performed ...

Page 58

... OSDT_CURX = 5 OSDT_CURY = 3 2004 Apr 01 OSDT_FR_X ... OSDT_WX (= 11) Fig.17 OSD window definition. OSDT_FR_Y zoom OSDT_WY (= 5) Fig.18 OSD window horizontal, vertical, flip, rotate. 58 Product specification SAA6703AH zoom picture ... MHC224 picture MHC225 OSDT_WY (= 5) OSDT_WX (= 11) ...

Page 59

... OSDT_SC_LO) that defines the multi or single character mapping inside the font RAM shadow fg_colour[2:0]/palette[2:0] DESCRIPTION 59 Product specification SAA6703AH bg_trans fg_trans bg_alpha ROM D0 fg_alpha charcode[8] ...

Page 60

... If that is not the case, the window RAM will ignore this part of the OSDT_PROP register and will keep up its previously defined value for this part at the selected OSD text window element fg_mask DESCRIPTION 60 Product specification SAA6703AH 2 C-bus write burst consisting code_mask write_mode[2:0] D0 ...

Page 61

... The real character contents are taken from either the font ROM/GEN part or the font RAM part of the OSD text indexed by that charcode. The font definition ROM/GEN is already providing a large amount of predefined fonts as illustrated in Fig.19. 61 Product specification SAA6703AH 2 I C-BUS SUBADDRESS AUTO-INCREMENT HANDLING OSDT_PROP0 etc. ...

Page 62

Acrobat reader. white to force landscape pages to be ... ...

Page 63

... ANSI like character set with ASCII mapping (ASCII code + 60H) single colour, basic Japanese font set single colour, border and line characters multicolour generated slider parts D3 D2 slider_offset[3:0] DESCRIPTION Product specification SAA6703AH D1 D0 ...

Page 64

... OSDT_PROP registers. Using multicolour definitions that need two bits per pixel and/or larger font resolution reduces of course the number of possible characters to be stored in the font RAM. 64 Product specification SAA6703AH offset gap OSDT_FR_Y colour 0 (BG) ...

Page 65

... Product specification SAA6703AH MAXIMUM NUMBER ...

Page 66

... To allow this, the SAA6703AH register auto-increment is re-addressing OSDT_CDEF after each write to OSDT_CDEF. Any changes to the OSD text RAM definitions can also be made while the OSD is displayed. So the usable character set is only limited by the size of the external microcontrollers ROM ...

Page 67

... OSDB_SX (= 12) Fig.22 OSD bitmap structure. USED DISPLAYABLE COLOURS PIXELS 2 32768 4 16384 16 8192 67 Product specification SAA6703AH picture OSDB_SY (= 11) MHC229 EXAMPLE WINDOW SIZES (NOT ZOOMED) 256 128; 181 181 256 64; 128 128 256 32 ...

Page 68

... In order to speed up the OSD bitmap definitions the internal RAM address is incremented by 8 bits always when a write to OSDB_DEF happened. Together with a stop of the SAA6703AH register auto-increment at this register, this allows a fast burst configuration of multiple pixel complete OSD bitmap definition setting the cursor to (0,0), the mask to FFH and writing all needed data bytes in a single burst ...

Page 69

... OSDP_DEF where the increment is depending on the actual used defwidth. Together with stopped SAA6703AH register auto-increment at OSDP_DEF, this allows a fast burst definition mode that needs 256 I to define a complete pointer buffer (see Table 47). ...

Page 70

... OSDP_CX = 20, OSDP_CY = 21 and OSDP_DW = 00 burst definition data bytes with OSDP_CX = 0, OSDP_CY = 0 and OSDP_DW = 11 Fig.24 Data format of the OSD pointer. USED BITS FROM OSDP_DEF 7 and Product specification SAA6703AH ... MHC231 NEEDED TRANSMISSIONS FOR A COMPLETE BUFFER 1024 512 342 256 ...

Page 71

... OSDT_PROP registers are written. To speed up clears or highlighting, the areafill function should be used. By setting the areafill_start bit, an area of the text window within the defined area boundaries is overwritten using the actual settings of OSDT_PROP[2:0] registers and the OSDT_MASK register. 71 Product specification SAA6703AH ...

Page 72

... The noise includes only one LSB if dither_noise_mag is set to logic 0; otherwise two LSBs. Configuration parameters dither_colmap, dither_rand_mono and dither_rand_mode are for test purposes and should be left in their reset values. 72 Product specification SAA6703AH SEQUENCE constant zero 2 2 Bayer 4 4 Bayer 5 ...

Page 73

... There are different possibilities how to map the RGB data to the output ports PA to PF. The SAA6703AH does not have particular output ports for panel signals VSYNC, HSYNC or DE. Instead, there are in total 5 Configurable Signal Generator (CSG) outputs which are driven by free programmable CSGs ...

Page 74

... OI_BLC_R, OI_BLC_G and OI_BLC_B OI_BOC_R, OI_BOC_G and OI_BOC_B 74 Product specification SAA6703AH VERTICAL active_start_y (OI_ASY) picture_start_y (OI_PSY) picture_end_y (OI_PEY) active_end_y (OI_AEY) last_line (OI_FY) LINE LENGTH REGISTER ...

Page 75

... The wait modes are programmed in register OI_WM according to Table 52. 1,1 picture area active frame main frame wait_column Fig.26 Wait column. no waiting waiting in each row of picture area waiting in first row of picture area once each frame 75 Product specification SAA6703AH blank_line_length MHC233 ACTION ...

Page 76

... If this bit is set to logic 1, then bit wise inversion of the colour component. Output port Px gets data byte with 6 bytes in double pixel mode or 3 bytes in single pixel mode (for F): 11X: 0R 101: 0G 100: 0B 01X: 1R 001: 1G 000 Product specification SAA6703AH PA MSB LSB MHC234 ACTION ...

Page 77

... There are 3 groups of CSGs. The CSGs of each group have some other additional features. in line mode the signal will be repeated in every line in the operation window b blank_line_length MHC235 Fig.28 Output frame set-up. 77 Product specification SAA6703AH action point in frame and line mode additional action points in line mode ...

Page 78

... Apr 01 last_line end_point (b) line based Fig.29 Examples for signal generator outputs line based frame based Fig.30 Examples for signal generator outputs. 78 Product specification SAA6703AH start_point (a) 1,1 end_point (b) frame based MHC236 hs hs end_point ( end_point ( ...

Page 79

... The output interface has four global modes, which can be programmed with bits OI_enable, power_down and blank_mode (register OI_CTRL0) according to Table 54. The blank colour is programmable via bits blank_colour_red, blank_colour_green and blank_colour_blue. 79 Product specification SAA6703AH CSG2 and CSG3 CSG4 ...

Page 80

... Table 58). The drive strength of control and clock signals are programmable individually. Table 57 Programmable drive strength DS2 Product specification SAA6703AH ACTION ROGRAMMABLE OUTPUT DRIVE STRENGTH DATA AND CONTROL DS1 DS0 OUTPUTS (mA 2 3.4 ...

Page 81

... Apr 01 DESCRIPTION from 2.9 mA (reset mA; see Table 57 from 5.8 mA (reset mA; see Table 57 BIT pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] PCLK_pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] pin_delay[4:0] 81 Product specification SAA6703AH REMARK OUTPUT PCLK CSG0 CSG1 CSG2 CSG3 CSG4 ...

Page 82

... BOUNDARY SCAN TEST The SAA6703AH has built-in logic and 5 dedicated pins to support boundary scan testing which allows board testing without special hardware (nails). The SAA6703AH follows the “IEEE Std. 1149.1 - Standard Test Access Port and Boundary-Scan Architecture” ...

Page 83

... Philips Semiconductors XGA analog input flat panel controller Table 60 BST instructions supported by the SAA6703AH INSTRUCTION BYPASS This mandatory instruction provides a minimum length serial path (1 bit) between TDI and TDO when no test operation of the component is required. EXTEST This mandatory instruction allows testing of off-chip circuitry and board level interconnections. ...

Page 84

... May not exceed 4.2 V; including outputs in 3-state mode; only when supply voltages are present. 2. Human body model 100 pF 1 Machine model 200 pF 0. THERMAL CHARACTERISTICS SYMBOL PARAMETER R thermal resistance from junction to ambient th(j-a) 2004 Apr 01 DDD(IC9 DDA(R) DDA( and DDA(ADC)(G) , DD(PLL)(P) DDA(PLL)(S) DDD(EP10) 84 SAA6703AH CONDITIONS MIN. 0.5 +3.3 0 2.8 0 2.8 0 3.3 0.5 +4.2 0 3.6 0.5 +5.8 note 1 0.5 V DDD(EP) 0.5 V DDA 1 ...

Page 85

... DDA(R) note 1 note AND DDA(PLL)(S) DDD(PLL)(S) note 1 note PIN DDA(IB) note 1 note DDD(EP1) DDD(EP10) note 1 note 1 note 1 note 1 BIN AND note 2 SOGIN 85 Product specification SAA6703AH MIN. TYP. MAX. 2.3 2.5 2.7 90 225 , DDA(G) DDA(B) DDA(ADC)(R) DDA(ADC)(G) 2.3 2.5 2.7 200 500 2.3 2.5 2 2.7 3.0 3 ...

Page 86

... PINS ) TOLERANT : PD0 PD7, PE0 PINS < V < DDD(EP) note 3 TDO SAA6703AH MIN. TYP. 25 110 8 0.8 1.6 6 500 40 96 TRST AND 0 0.7 1.7 V DDD(EP 0 PE7, PF0 PF7, CSG0, CSG1, CSG3, PCLK, ...

Page 87

... DDD(EP) note 3 : VSYNC PIN note DDD(EP tolerant 5 V tolerant SAA6703AH MIN. TYP. : PA0 PA7, PB0 PINS TO 0 0.8 2.0 3.6 0 0.4 V 0.4 V DDD(EP) DDD(EP 0.8 2.0 5.5 0 0.4 V 0.4 V DDD(EP) DDD(EP) ...

Page 88

... PCLK to output delay out2 time; double pixel mode t output delay increment del 2004 Apr 01 attenuator 5 CONDITIONS MIN 2/f VCLK 2/f VCLK 3.5 L 200 88 Product specification SAA6703AH TYP. MAX. UNIT 41. +0.2 ns 0.8 ns 500 800 ps ...

Page 89

... XGA analog input flat panel controller handbook, full pagewidth VCLK HSYNC, VSYNC handbook, full pagewidth VCLK PA, PB, PC 2004 Apr Fig.33 Analog video interface timing Fig.34 Parallel video interface timing. 89 Product specification SAA6703AH MHC240 MHC241 ...

Page 90

... XGA analog input flat panel controller PCLK PA, PB, PC, PD, PE, PF, CSG undelayed, single pixel mode PA, PB, PC, PD, PE, PF, CSG undelayed, double pixel mode delayed 2004 Apr out1 t out2 out del Fig.35 Panel interface timing. 90 Product specification SAA6703AH mhc691 ...

Page 91

... Philips Semiconductors XGA analog input flat panel controller 13 APPLICATION INFORMATION 2004 Apr 01 VGA SAA6703AH PORT 2 I C-bus MICROCONTROLLER EEPROM Fig.36 Application board block diagram. 91 Product specification SAA6703AH PANEL CONNECTOR USB col014 ...

Page 92

... scale (1) ( 0.38 0.23 28.1 28.1 31.45 31.45 0.65 0.22 0.13 27.9 27.9 30.95 30.95 REFERENCES JEDEC JEITA MS-022 detail 1.03 1.5 0.13 0.1 1.6 0.3 0.73 1.1 EUROPEAN PROJECTION Product specification SAA6703AH SOT322 ( 1.1 0 ISSUE DATE 00-01-19 03-02-25 ...

Page 93

... Use a low voltage ( less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds 300 C. When using a dedicated tool, all other leads can be soldered in one operation within seconds between 270 and 320 C. 93 Product specification SAA6703AH ...

Page 94

... Hot bar or manual soldering is suitable for PMFP packages. 2004 Apr 01 (1) (3) , TFBGA, VFBGA not suitable not suitable suitable not recommended not recommended not suitable 94 Product specification SAA6703AH SOLDERING METHOD (2) WAVE REFLOW suitable (4) suitable suitable (5)(6) suitable (7) suitable not suitable ...

Page 95

... Product specification SAA6703AH DEFINITION These products are not Philips Semiconductors ...

Page 96

... Philips. This specification can be ordered using the code 9398 393 40011. 2004 Apr 01 C COMPONENTS 2 C components conveys a license under the Philips’ system provided the system conforms to the I 96 Product specification SAA6703AH 2 C patent to use the 2 C specification defined by ...

Page 97

Philips Semiconductors – a worldwide company Contact information For additional information please visit http://www.semiconductors.philips.com. For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com. © Koninklijke Philips Electronics N.V. 2004 All rights are reserved. Reproduction in whole or in part is prohibited ...