A3985SLDTR-T Allegro Microsystems Inc, A3985SLDTR-T Datasheet - Page 10

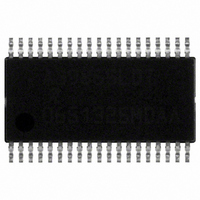

A3985SLDTR-T

Manufacturer Part Number

A3985SLDTR-T

Description

IC MOSFET DRVR PROG DUAL 38TSSOP

Manufacturer

Allegro Microsystems Inc

Datasheet

1.A3985SLDTR-T.pdf

(15 pages)

Specifications of A3985SLDTR-T

Configuration

H Bridge

Input Type

Non-Inverting

Delay Time

120ns

Number Of Configurations

2

Number Of Outputs

8

Voltage - Supply

12 V ~ 50 V

Operating Temperature

-20°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

38-TSSOP

Device Type

Full Bridge

Module Configuration

Full Bridge

Peak Output Current

500nA

Output Resistance

19ohm

Input Delay

120ns

Output Delay

120ns

Supply Voltage Range

12V To 50V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Peak

-

High Side Voltage - Max (bootstrap)

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

620-1180-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

A3985SLDTR-T

Manufacturer:

ALLEGRO/雅丽高

Quantity:

20 000

A3985

gramming the Fast Decay Time bits in the Control register

(Word1, Bits D8 through D11). If t

the device effectively operates in full fast decay mode.

Selecting between slow decay and mixed decay is done by

programming the Mode bits in the Data register (Word0, Bits

D8 and D16) using the serial port.

Synchronous Rectification

is triggered, load current recirculates according to the decay

mode selected by the control logic. The synchronous rectifi-

cation feature turns on the appropriate MOSFETs during the

current decay and effectively shorts out the body diodes with

the low R

sipation significantly and eliminates the need for additional

Schottky diodes.

Synchronous rectification can be set to one of three distinct

modes by programming the Synchronous Rectification bits

in the Control register (Word1, Bits D14 through D15) using

the serial port. The modes are:

Shutdown Operation

ture fault, or an undervoltage fault on VREG, the gate drive

outputs are disabled until the fault condition is removed.

At power-up, and in the event of low voltage at VDD, the

under voltage lockout (UVLO) circuit disables the gate drive

outputs until the voltage at VDD reaches the minimum level.

Once VDD is above the minimum level, the data in the serial

port is reset to all 0s, ensuring a safe power-up condition.

Serial Interface

The A3985 is controlled by a 3-wire serial port using data,

clock and strobe inputs on the SDI, SCK and STR pins

respectively. An additional serial data output on SDO can

• Active This mode prevents reversal of the load current by

• Passive This mode allows reversal of current, but will

• Disabled During this mode, MOSFET switching does not

turning off synchronous rectification when a zero current

level is detected. This prevents the motor winding from

conducting in the reverse direction.

turn of the synchronous rectifier circuit if the load current

inversion ramps up to the current limit, I

occur during load recirculation. Usually, this setting would

only be used with 4 additional external clamp diodes per

bridge.

DS(ON)

of the MOSFET. This lowers power dis-

In the event of an overtempera-

FD

When a PWM off-cycle

is set longer than t

TripDAC

.

OFF

Dual Full-Bridge MOSFET Driver

,

be used to connect several A3985s in a serial daisy chain.

The programmable functions allow maximum flexibility in

configuring the PWM to the motor drive requirements. The

serial data is written as two 19-bit words: 18 bits of data plus

1 bit to select the destination register.

Serial Port Write Timing Operation The serial port tim-

ing requirements are specified in the electrical characteristics

table, and illustrated in the Serial Data Timing diagram.

Data is received on the SDI pin and clocked through a shift

register on the rising edge of the clock signal received on the

SCK pin. STR is normally held high, and is only brought low

to initiate a write cycle. No data is clocked through the shift

register when STR is high.

The 18 data bits for a register are input MSB first, fol-

lowed by the register select bit, D0. After D0 is clocked

into the shift register, STR goes high to latch the data into

the selected register. When this occurs, the internal control

circuits immediately act on the new data.

The Control register can only be written if the WC pin is at

logic low. If WC is high and D0 = 1 (indicating the Control

register), the data will be ignored on the rising edge of STR.

The state of the WC pin does not affect writing to the Data

register, and the pin can be tied to GND when Control regis-

ter protection is not required.

Note that the number of bits clocked through the shift reg-

ister is irrelevant and only the last 19 bits before STR goes

high will be latched. This allows several A3985 devices to be

daisy-chained and updated together with a single STR rising

edge.

Data Register (Word 0) Bit Assignments

This section describes the function of the individual bit

values in the Data register, one of the two registers accessed

through the serial port. The assignments are summarized in

the Bit Assignments table.

D0 – Register Select Indicates which register should

receive the data. For the Data register, this is set to 0.

D1 through D6 – Bridge 1 Linear DAC These six bits

set the desired current level for Bridge 1. Setting all six bits

Digitally Programmable

115 Northeast Cutoff

1.508.853.5000; www.allegromicro.com

Allegro MicroSystems, Inc.

Worcester, Massachusetts 01615-0036 U.S.A.

10