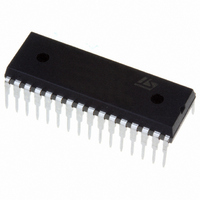

ST72F63BK4B1 STMicroelectronics, ST72F63BK4B1 Datasheet - Page 101

ST72F63BK4B1

Manufacturer Part Number

ST72F63BK4B1

Description

IC MCU 8BIT 16K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F63BD6U1TR.pdf

(186 pages)

Specifications of ST72F63BK4B1

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, SCI, USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

19

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 12x8b

Oscillator Type

External

Operating Temperature

0°C ~ 70°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F6x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

I2C, SCI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

19

Number Of Timers

1

Maximum Operating Temperature

+ 70 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7MDTU3-EPB/US, ST72F63B-SK/RAIS, ST7MDTU3-EMU3, STX-RLINK

Minimum Operating Temperature

0 C

On-chip Adc

8 bit, 8 Channel / 8 bit, 12 Channel

For Use With

497-5521 - EVAL BOARD LOW SPEED USB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

- Current page: 101 of 186

- Download datasheet (3Mb)

ST7263Bxx

Note:

Interrupt Status register (ISTR)

Reset value: 0000 0000 (00h)

When an interrupt occurs these bits are set by hardware. Software must read them to

determine the interrupt type and clear them after servicing.

These bits cannot be set by software.

SUSP

7

7 SUSP Suspend mode request.

6 DOVR DMA over/underrun.

5 CTR Correct Transfer. This bit is set by hardware when a correct transfer operation

4 ERR Error.

3 IOVR Interrupt overrun.

DOVR

This bit is set by hardware when a constant idle state is present on the bus line for

more than 3 ms, indicating a suspend mode request from the USB bus. The

suspend request check is active immediately after each USB reset event and its

disabled by hardware when suspend mode is forced (FSUSP bit of CTLR register)

until the end of resume sequence.

This bit is set by hardware if the ST7 processor can’t answer a DMA request in

time.

0: No over/underrun detected

1: Over/underrun detected

is performed. The type of transfer can be determined by looking at bits TP3-TP2 in

register PIDR. The Endpoint on which the transfer was made is identified by bits

EP1-EP0 in register IDR.

0: No Correct Transfer detected

1: Correct Transfer detected

Note: A transfer where the device sent a NAK or STALL handshake is considered

This bit is set by hardware whenever one of the errors listed below has occurred:

0: No error detected

1: Timeout, CRC, bit stuffing or nonstandard

framing error detected

This bit is set when hardware tries to set ERR, or SOF before they have been

cleared by software.

0: No overrun detected

1: Overrun detected

not correct (the host only sends ACK handshakes). A transfer is considered

correct if there are no errors in the PID and CRC fields, if the DATA0/DATA1

PID is sent as expected, if there were no data overruns, bit stuffing or

framing errors.

CTR

Doc ID 7516 Rev 8

ERR

Read.write

IOVR

ESUSP

On-chip peripherals

RESET

101/186

SOF

0

Related parts for ST72F63BK4B1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER LOW COST ST7

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

LOW SPEED USB 8-BIT MCU FAMILY WITH FLASH/ROM, UP TO 512 BYTES RAM, 8-BIT ADC, WDG, TIMER, SCI & I�C

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: