ST72F63BK4B1 STMicroelectronics, ST72F63BK4B1 Datasheet - Page 105

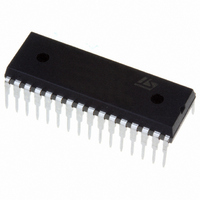

ST72F63BK4B1

Manufacturer Part Number

ST72F63BK4B1

Description

IC MCU 8BIT 16K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F63BD6U1TR.pdf

(186 pages)

Specifications of ST72F63BK4B1

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, SCI, USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

19

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 12x8b

Oscillator Type

External

Operating Temperature

0°C ~ 70°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F6x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

I2C, SCI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

19

Number Of Timers

1

Maximum Operating Temperature

+ 70 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7MDTU3-EPB/US, ST72F63B-SK/RAIS, ST7MDTU3-EMU3, STX-RLINK

Minimum Operating Temperature

0 C

On-chip Adc

8 bit, 8 Channel / 8 bit, 12 Channel

For Use With

497-5521 - EVAL BOARD LOW SPEED USB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

- Current page: 105 of 186

- Download datasheet (3Mb)

ST7263Bxx

Note:

Endpoint n register B (EPnRB)

These registers (EP1RB and EP2RB) are used for controlling data reception on Endpoints 1

and 2. They are also reset by the USB bus reset.

Endpoint 2 and the EP2RB register are not available on some devices (see device feature

list and register map).

Reset value: 0000 xxxx (0xh)

Table 35.

CTRL

STAT_RX1

7

0

0

1

1

[5:4] STAT_RX [1:0] Status bits, for reception transfers.

[3:0] EA[3:0] Endpoint address.

STAT_RX bit definition

7 CTRL Control.

6 DTOG_RX Data toggle, for reception transfers.

This bit should be 0.

Note: If this bit is 1, the Endpoint is a control endpoint. (Endpoint 0 is always a

It contains the expected value of the toggle bit (0=DATA0, 1=DATA1) for the next

data packet. This bit is cleared by hardware in the first stage (Setup Stage) of a

control transfer (SETUP transactions start always with DATA0 PID). The receiver

toggles DTOG_RX only if it receives a correct data packet and the packet’s data

PID matches the receiver sequence bit.

These bits contain the information about the endpoint status, which are listed in

Table

These bits are written by software. Hardware sets the STAT_RX bits to NAK when a

correct transfer has occurred (CTR=1) related to an OUT or SETUP transaction

addressed to this endpoint, so the software has the time to elaborate the received

data before acknowledging a new transaction.

Software must write in this field the 4-bit address used to identify the transactions

directed to this endpoint. Usually EP1RB contains “0001” and EP2RB contains

“0010”.

DTOG

_RX

35.

control Endpoint, but it is possible to have more than one control Endpoint).

STAT_RX0

Doc ID 7516 Rev 8

_RX1

STAT

0

1

0

1

Read.write

_RX0

STAT

DISABLED: reception transfers cannot be

executed.

STALL: the endpoint is stalled and all reception

requests result in a STALL handshake.

NAK: the endpoint is naked and all reception

requests result in a NAK handshake.

VALID: this endpoint is enabled for reception.

EA3

Meaning

EA2

On-chip peripherals

EA1

105/186

EA0

0

Related parts for ST72F63BK4B1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER LOW COST ST7

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

LOW SPEED USB 8-BIT MCU FAMILY WITH FLASH/ROM, UP TO 512 BYTES RAM, 8-BIT ADC, WDG, TIMER, SCI & I�C

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: