D12321VF20V Renesas Electronics America, D12321VF20V Datasheet - Page 1115

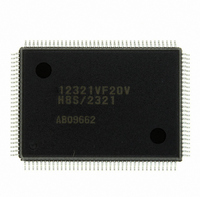

D12321VF20V

Manufacturer Part Number

D12321VF20V

Description

IC H8S/2321 MCU ROMLESS 128QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2300r

Specifications of D12321VF20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

SCI, SmartCard

Peripherals

POR, PWM, WDT

Number Of I /o

86

Program Memory Type

ROMless

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

128-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D12321VF20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1115 of 1304

- Download datasheet (8Mb)

TIOR3L—Timer I/O Control Register 3L

Bit

Initial value

Read/Write

Note: When TGRC or TGRD is designated for buffer operation, this setting is invalid and the

register operates as a buffer register.

:

:

:

Notes:

TGR3D I/O Control

0

1

IOD3

R/W

7

0

0

1

0

1

1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000 and φ/1 is used as

2. When the BFB bit in TMDR3 is set to 1 and TGR3D is used as a buffer

0

1

0

1

0

1

*

the TCNT4 count clock, this setting is invalid and input capture does not

occur.

register, this setting is invalid and input capture/output compare does not

occur.

IOD2

R/W

6

0

0

1

0

1

0

1

0

1

0

1

*

*

TGR3D

is output

compare

register

*

TGR3D

is input

capture

register

*

2

2

IOD1

R/W

5

0

Output disabled

Initial output is 0

output

Output disabled

Initial output is 1

output

Capture input

source is

TIOCD

Capture input

source is channel

4/count clock

Note: 1. When the BFA bit in TMDR3 is set to 1 and TGR3C is used as a buffer

TGR3C I/O Control

IOD0

R/W

0

1

4

0

3

pin

0

1

0

1

register, this setting is invalid and input capture/output compare does not

occur.

IOC3

0

1

0

1

0

1

*

R/W

3

0

1 output at compare match

Toggle output at compare match

1 output at compare match

Toggle output at compare match

Input capture at rising edge

Input capture at falling edge

Input capture at both edges

0 output at compare match

0 output at compare match

Input capture at TCNT4 count-up/

count-down *

0

1

0

1

0

1

0

1

0

1

*

*

TGR3C

is output

compare

register*

TGR3C

is input

capture

register*

IOC2

R/W

2

0

Rev.6.00 Sep. 27, 2007 Page 1083 of 1268

H'FE83

1

1

1

Output disabled

Initial output is

0 output

Output disabled

Initial output is 1

output

Capture input

source is

TIOCC

Capture input

source is channel

4/count clock

IOC1

R/W

1

0

3

* : Don’t care

pin

Appendix B Internal I/O Registers

IOC0

R/W

0

0

1 output at compare match

Toggle output at compare match

1 output at compare match

Toggle output at compare match

Input capture at rising edge

Input capture at falling edge

Input capture at both edges

0 output at compare match

0 output at compare match

Input capture at TCNT4 count-up/

count-down

REJ09B0220-0600

* : Don’t care

TPU3

Related parts for D12321VF20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: