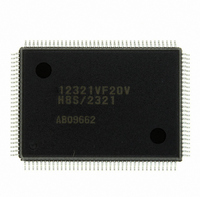

D12321VF20V Renesas Electronics America, D12321VF20V Datasheet - Page 312

D12321VF20V

Manufacturer Part Number

D12321VF20V

Description

IC H8S/2321 MCU ROMLESS 128QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2300r

Specifications of D12321VF20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

SCI, SmartCard

Peripherals

POR, PWM, WDT

Number Of I /o

86

Program Memory Type

ROMless

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

128-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D12321VF20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 312 of 1304

- Download datasheet (8Mb)

Section 7 DMA Controller (Not Supported in the H8S/2321)

unless the prescribed register is accessed in a DMA transfer. If the same interrupt is used as an

activation source for more than one channel, the interrupt request flag is cleared when the highest-

priority channel is activated first. Transfer requests for other channels are held pending in the

DMAC, and activation is carried out in order of priority.

When DTE = 0, such as after completion of a transfer, a request from the selected activation

source is not sent to the DMAC, regardless of the DTA bit. In this case, the relevant interrupt

request is sent to the CPU or DTC.

In case of overlap with a CPU interrupt source or DTC activation source (DTA = 0), the interrupt

request flag is not cleared by the DMAC.

Activation by External Request: If an external request (DREQ pin) is specified as an activation

source, the relevant port should be set to input mode in advance.

Level sensing or edge sensing can be used for external requests.

External request operation in normal mode (short address mode or full address mode) is described

below.

When edge sensing is selected, a 1-byte or 1-word transfer is executed each time a high-to-low

transition is detected on the DREQ pin. The next transfer may not be performed if the next edge is

input before transfer is completed.

When level sensing is selected, the DMAC stands by for a transfer request while the DREQ pin is

held high. While the DREQ pin is held low, transfers continue in succession, with the bus being

released each time a byte or word is transferred. If the DREQ pin goes high in the middle of a

transfer, the transfer is interrupted and the DMAC stands by for a transfer request.

Activation by Auto-Request: Auto-request activation is performed by register setting only, and

transfer continues to the end.

With auto-request activation, cycle steal mode or burst mode can be selected.

In cycle steal mode, the DMAC releases the bus to another bus master each time a byte or word is

transferred. DMA and CPU cycles usually alternate.

In burst mode, the DMAC keeps possession of the bus until the end of the transfer, and transfer is

performed continuously.

Single Address Mode: The DMAC can operate in dual address mode in which read cycles and

write cycles are separate cycles, or single address mode in which read and write cycles are

executed in parallel.

Rev.6.00 Sep. 27, 2007 Page 280 of 1268

REJ09B0220-0600

Related parts for D12321VF20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: