D12321VF20V Renesas Electronics America, D12321VF20V Datasheet - Page 290

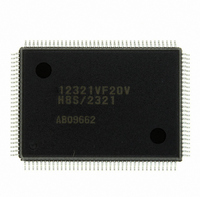

D12321VF20V

Manufacturer Part Number

D12321VF20V

Description

IC H8S/2321 MCU ROMLESS 128QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2300r

Specifications of D12321VF20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

SCI, SmartCard

Peripherals

POR, PWM, WDT

Number Of I /o

86

Program Memory Type

ROMless

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

128-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D12321VF20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 290 of 1304

- Download datasheet (8Mb)

Section 7 DMA Controller (Not Supported in the H8S/2321)

MAR specifies the start address of the transfer source or transfer destination as 24 bits. MAR is

incremented or decremented by 1 or 2 each time a byte or word is transferred.

IOAR specifies the lower 16 bits of the other address. The 8 bits above IOAR have a value of

H'FF.

Figure 7.3 illustrates operation in sequential mode.

The number of transfers is specified as 16 bits in ETCR. ETCR is decremented by 1 each time a

transfer is executed, and when its value reaches H'0000, the DTE bit is cleared and transfer ends.

If the DTIE bit is set to 1 at this time, an interrupt request is sent to the CPU or DTC.

The maximum number of transfers, when H'0000 is set in ETCR, is 65,536.

Rev.6.00 Sep. 27, 2007 Page 258 of 1268

REJ09B0220-0600

Address T

Address B

Figure 7.3 Operation in Sequential Mode

Transfer

1 byte or word transfer performed in

response to 1 transfer request

Legend:

Address T = L

Address B = L + (–1)

Where : L = Value set in MAR

N = Value set in ETCR

DTID

· (2

DTSZ

· (N–1))

IOAR

Related parts for D12321VF20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: