MC908AZ60AVFUE Freescale Semiconductor, MC908AZ60AVFUE Datasheet - Page 140

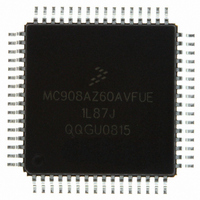

MC908AZ60AVFUE

Manufacturer Part Number

MC908AZ60AVFUE

Description

IC MCU 61K FLASH 8.4MHZ 64-QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908AZ60ACFUER.pdf

(414 pages)

Specifications of MC908AZ60AVFUE

Core Processor

HC08

Core Size

8-Bit

Speed

8.4MHz

Connectivity

CAN, SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

52

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 15x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

64-QFP

Processor Series

HC08AZ

Core

HC08

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SCI, SPI

Maximum Clock Frequency

8.4 MHz

Number Of Programmable I/os

52

Number Of Timers

8

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05CE, ZK-HC08AX-A, M68EM08AS/AZ60AE

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 15 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AZ60AVFUE

Manufacturer:

FREESCALE

Quantity:

2 500

Company:

Part Number:

MC908AZ60AVFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC908AZ60AVFUE

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC908AZ60AVFUER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 140 of 414

- Download datasheet (5Mb)

Clock Generator Module (CGM)

10.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

10.7.1 Wait Mode

The CGM remains active in wait mode. Before entering wait mode, software can disengage and turn off

the PLL by clearing the BCS and PLLON bits in the PLL control register (PCTL). Less power-sensitive

applications can disengage the PLL without turning it off. Applications that require the PLL to wake the

MCU from wait mode also can deselect the PLL output without turning off the PLL.

10.7.2 Stop Mode

The STOP instruction disables the CGM and holds low all CGM outputs (CGMXCLK, CGMOUT, and

CGMINT).

If CGMOUT is being driven by CGMVCLK and a STOP instruction is executed; the PLL will clear the BCS

bit in the PLL control register, causing CGMOUT to be driven by CGMXCLK. When the MCU recovers

from STOP, the crystal clock divided by two drives CGMOUT and BCS remains clear.

10.8 CGM During Break Interrupts

The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the

break state. See

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status

bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the PLLF bit during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its

default state), software can read and write the PLL control register during the break state without affecting

the PLLF bit.

10.9 Acquisition/Lock Time Specifications

The acquisition and lock times of the PLL are, in many applications, the most critical PLL design

parameters. Proper design and use of the PLL ensures the highest stability and lowest acquisition/lock

times.

10.9.1 Acquisition/Lock Time Definitions

Typical control systems refer to the acquisition time or lock time as the reaction time, within specified

tolerances, of the system to a step input. In a PLL, the step input occurs when the PLL is turned on or

when it suffers a noise hit. The tolerance is usually specified as a percent of the step input or when the

output settles to the desired value plus or minus a percent of the frequency change. Therefore, the

reaction time is constant in this definition, regardless of the size of the step input. For example, consider

a system with a 5% acquisition time tolerance. If a command instructs the system to change from 0 Hz to

140

Software can select the CGMVCLK divided by two as the CGMOUT source

even if the PLL is not locked (LOCK = 0). Therefore, software should make

sure the PLL is locked before setting the BCS bit.

Chapter 13 Break Module

MC68HC908AZ60A • MC68HC908AS60A • MC68HC908AS60E Data Sheet, Rev. 6

(BRK).

NOTE

Freescale Semiconductor

Related parts for MC908AZ60AVFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: