CDB3318 Cirrus Logic Inc, CDB3318 Datasheet - Page 28

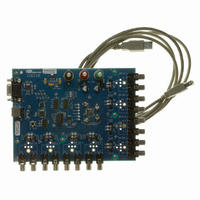

CDB3318

Manufacturer Part Number

CDB3318

Description

Eval Bd - 8-channel Digital Vol Cntrl

Manufacturer

Cirrus Logic Inc

Specifications of CDB3318

Main Purpose

Audio, Volume Control

Embedded

No

Utilized Ic / Part

CS3318

Primary Attributes

8 Single-Ended Analog Inputs and Outputs, USB or RS232 Interface

Secondary Attributes

Graphical User Interface

Description/function

Audio DSPs

Operating Supply Voltage

8 V to 9 V

Product

Audio Modules

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

CS3310

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant, Contains lead / RoHS non-compliant

Other names

598-1497

28

5.9.2

SCL

SDA

Since the read operation cannot set the MAP, an aborted write operation is used as a preamble. As shown

in

dition.

SPI Mode

In SPI Mode, CS is the CS3318 chip-select signal, CCLK, is the control port bit clock (input into the

CS3318 from the microcontroller), and MOSI is the input data line from the microcontroller. Data is

clocked in on the rising edge of CCLK. The default chip address in SPI Mode is 1000000b.

Figure 14

first seven bits on MOSI form the chip address and must be either the Individual, Group 1, or Group 2 chip

address as set by their respective control port registers. The eighth bit is a read/write indicator (R/W),

which must be low to write. If the read/write indicator is set high (indicating a read operation), the CS3318

will ignore all traffic on the SPI bus until CS is brought high and then low again. The next eight bits form

the Memory Address Pointer (MAP), which is set to the address of the register that is to be written. The

next eight bits are the data which will be placed into the register designated by the MAP.

There is a MAP auto increment capability, enabled by the INCR bit (the MSB of the MAP byte). If INCR is

‘0’, the MAP will stay constant for successive read or writes. If INCR is ‘1’, the MAP will automatically in-

crement after each byte is written, allowing block writes of successive registers.

Referenced Control

Individual Address...............

Group 1 Address .................

Group 2 Address .................

Referenced Control

Individual Address...............

Group 1 Address .................

Group 2 Address .................

Figure

MOSI

CCLK

START

CS

MSB

13, the write operation is aborted after the acknowledge for the MAP byte by sending a stop con-

0

CHIP ADDRESS (WRITE)

shows the operation of the control port in SPI Mode. To write to a register, bring CS low. The

1

Chip Address

2

MSB

3

4

5

LSB

Chip Address

Register Location

Register Location

6

“Individual Chip Address 1Bh” on page 41

“Group 1 Chip Address 1Ah” on page 40

“Group 2 Chip Address 19h” on page 40

“Individual Chip Address 1Bh” on page 41

“Group 1 Chip Address 1Ah” on page 40

“Group 2 Chip Address 19h” on page 40

1 Byte

7

0

ACK

Figure 13. Control Port Timing, I²C Read

8

9

INCR

10 11

6

Figure 14. SPI Write Cycle

LSB

5

MAP BYTE

12 13 14 15

4

W

3

INCR

2

1

MSB

16

0

ACK

STOP

17 18

START

Memory Address Pointer

1 Byte

19

MSB

20 21 22 23 24

CHIP ADDRESS (READ)

Chip Address

LSB

LSB

25

26 27 28

MSB

1

ACK

7

DATA

0

ACK

> 1 Byte

Data

DATA +1

7

0

DATA + n

7

CS3318

0

LSB

ACK

NO

DS693F1

STOP