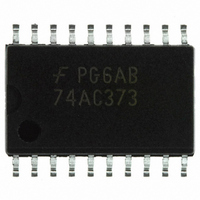

74AC373SC Fairchild Semiconductor, 74AC373SC Datasheet

74AC373SC

Specifications of 74AC373SC

Available stocks

Related parts for 74AC373SC

74AC373SC Summary of contents

Page 1

... Features I and I reduced by 50 Eight latches in a single package 3-STATE outputs for bus interfacing Outputs source/sink 24mA ACT373 has TTL-compatible inputs Ordering Information Package Order Number Number 74AC373SC M20B 74AC373SJ M20D 74AC373MTC MTC20 74AC373PC N20A 74ACT373SC M20B 74ACT373SJ M20D 74ACT373MSA MSA20 ...

Page 2

... When OE is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches. ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5.0 Logic Symbols IEEE/IEC Truth Table ...

Page 3

... Logic Diagram Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5.0 3 www.fairchildsemi.com ...

Page 4

... I V Output Voltage O T Operating Temperature Minimum Input Edge Rate, AC Devices: V from 30 Minimum Input Edge Rate, ACT Devices: V from 0.8V to 2.0V ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5.0 Parameter Parameter , V @ 3.3V, 4.5V, 5. 4.5V, 5. Rating 0.5V to 7.0V 20mA 20mA 0. 0.5V ...

Page 5

... Notes: 1. All outputs loaded; thresholds on input associated with output under test and I @ 3.0V are guaranteed to be less than or equal to the respective limit @ 5. Maximum test duration 2.0ms, one output loaded at a time. ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5 (V) Conditions Typ. ...

Page 6

... OLD (5) Output Current I OHD I Maximum Quiescent CC Supply Current Notes: 4. All outputs loaded; thresholds on input associated with output under test. 5. Maximum test duration 2.0ms, one output loaded at a time. ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5 (V) Conditions Typ. CC 4.5 V 0.1V or 1.5 ...

Page 7

... Voltage range 5.0 is 5.0V AC Operating Requirements for AC Symbol Parameter t Setup Time, HIGH or LOW Hold Time, HIGH or LOW Pulse Width, HIGH W Note: 7. Voltage range 3.3 is 3.3V 0.3V. Voltage range 5.0 is 5.0V ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5 50pF L (6) V (V) Min. Typ 3.3 1 ...

Page 8

... Setup Time, HIGH or LOW Hold Time, HIGH or LOW Pulse Width, HIGH W Note: 9. Voltage range 5.0 is 5.0V 0.5V. Capacitance Symbol Parameter C Input Capacitance IN C Power Dissipation Capacitance PD ©1988 Fairchild Semiconductor Corporation 74AC373, 74ACT373 Rev. 1.5 50pF L (8) V (V) Min. Typ 5.0 2.5 8 5.0 2.0 8 ...

Page 9

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 10

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 11

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 12

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 13

... Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifi ...

Page 14

... TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended exhaustive list of all such trademarks. ® ACEx Build it Now™ CorePLUS™ CROSSVOLT™ CTL™ Current Transfer Logic™ ...