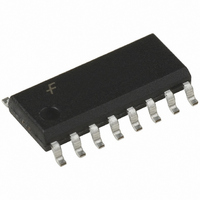

ML4824CS1 Fairchild Semiconductor, ML4824CS1 Datasheet - Page 10

ML4824CS1

Manufacturer Part Number

ML4824CS1

Description

IC PFC PWM CTRLR COMBO 16-SOIC

Manufacturer

Fairchild Semiconductor

Datasheet

1.ML4824IP1.pdf

(15 pages)

Specifications of ML4824CS1

Mode

Average Current

Frequency - Switching

76kHz

Current - Startup

700µA

Voltage - Supply

10.5 V ~ 13.2 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

16-SOIC (0.300", 7.5mm Width)

Switching Frequency

81 KHz

Maximum Operating Temperature

+ 150 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 65 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

ML4824

V

The V

and inhibits the PWM if this voltage on V

its nominal 2.5V. Once this voltage reaches 2.5V, which

corresponds to the PFC output capacitor being charged to its

rated boost voltage, the soft-start begins.

PWM Control (RAMP 2)

When the PWM section is used in current mode, RAMP 2 is

generally used as the sampling point for a voltage represent-

ing the current in the primary of the PWM’s output trans-

former, derived either by a current sensing resistor or a

current transformer. In voltage mode, it is the input for a

ramp voltage generated by a second set of timing compo-

nents (R

value of zero volts and should have a peak value of approxi-

mately 5V. In voltage mode operation, feedforward from the

PFC output buss is an excellent way to derive the timing

ramp for the PWM stage.

Soft Start

Start-up of the PWM is controlled by the selection of the

external capacitor at SS. A current source of 50µA supplies

the charging current for the capacitor, and start-up of the

PWM begins at 1.25V. Start-up delay can be programmed by

the following equation::

where C

is the desired start-up delay.

It is important that the time constant of the PWM soft-start

allow the PFC time to generate sufficient output power for

the PWM section. The PWM start-up delay should be at least

5ms.

Solving for the minimum value of C

Caution should be exercised when using this minimum soft

start capacitance value because premature charging of the SS

capacitor and activation of the PWM section can result if

V

start-up. The magnitude of V

line voltage and nominal PFC output voltage. Typically, a

1.0 F soft start capacitor will allow time for V

out to reach their nominal values prior to activation of the

PWM section at line voltages between 90Vrms and

265Vrms.

GENERATING V

The ML4824 is a current-fed part. It has an internal shunt

voltage regulator, which is designed to regulate the voltage

internal to the part at 13.5V. This allows a low power dissipa-

tion while at the same time delivering 10V of gate drive at

the PWM OUT and PFC OUT outputs. It is important to

10

IN

FB

C

C

OK Comparator

SS

SS

is in the hysteresis band of the V

IN

=

RAMP2

=

SS

OK comparator monitors the DC output of the PFC

5ms

t

DELAY

is the required soft start capacitance, and t

CC

, C

--------------- -

1.25V

50 A

RAMP2

--------------- -

1.25V

50 A

=

), which will have a minimum

200nF

FB

at start-up is related both to

SS

IN

:

OK comparator at

FB

is less than

FB

and PFC

DELAY

(6)

limit the current through the part to avoid overheating or

destroying it. This can be easily done with a single resistor in

series with the Vcc pin, returned to a bias supply of typically

18V to 20V. The resistor’s value must be chosen to meet the

operating current requirement of the ML4824 itself (19mA

max) plus the current required by the two gate driver outputs.

EXAMPLE:

With a V

ML4824 driving a total gate charge of 110nC at 100kHz

(e.g., 1 IRF840 MOSFET and 2 IRF830 MOSFETs), the

gate driver current required is:

To check the maximum dissipation in the ML4824, find the

current at the minimum V

The maximum allowable I

able design.

The ML4824 should be locally bypassed with a 10nF and a

1 F ceramic capacitor. In most applications, an electrolytic

capacitor of between 100 F and 330 F is also required

across the part, both for filtering and as part of the start-up

bootstrap circuitry.

Leading/Trailing Modulation

Conventional Pulse Width Modulation (PWM) techniques

employ trailing edge modulation in which the switch will

turn on right after the trailing edge of the system clock.

The error amplifier output voltage is then compared with the

modulating ramp. When the modulating ramp reaches the

level of the error amplifier output voltage, the switch will be

turned OFF. When the switch is ON, the inductor current will

ramp up. The effective duty cycle of the trailing edge modu-

lation is determined during the ON time of the switch. Figure

4 shows a typical trailing edge control scheme.

I

R

I

Figure 3. External Component Connections to V

GATEDRIVE

CC

BIAS

=

BIAS

=

20V 12.4V

-------------------------------- -

-------------------------------------- -

19mA

180

20V 14.6V

ML4824

of 20V, a V

V BIAS

–

V CC

GND

=

100kHz 100nC

–

R BIAS

+

11mA

=

CC

CC

42.2mA

CC

CERAMIC

=

(12.4V)::

limit of 14.6V (max) and the

10nF

is 55mA, so this is an accept-

180

PRODUCT SPECIFICATION

=

11mA

CERAMIC

REV. 1.0.6 11/7/03

1 F

CC

(7)

(8)

(9)