ISL6545ACRZ Intersil, ISL6545ACRZ Datasheet - Page 6

ISL6545ACRZ

Manufacturer Part Number

ISL6545ACRZ

Description

IC PWM BUCK BST VM 10DFN

Manufacturer

Intersil

Datasheet

1.ISL6545ACBZ-T.pdf

(16 pages)

Specifications of ISL6545ACRZ

Pwm Type

Voltage Mode

Number Of Outputs

1

Frequency - Max

660kHz

Duty Cycle

100%

Voltage - Supply

4.5 V ~ 14.4 V

Buck

Yes

Boost

Yes

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

10-DFN

Frequency-max

660kHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Functional Description

Initialization (POR and OCP Sampling)

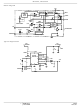

Figure 1 shows a simplified timing diagram. The

Power-On-Reset (POR) function continually monitors the

bias voltage at the VCC pin. Once the rising POR threshold

is exceeded (VPOR ~4V nominal), the POR function initiates

the Overcurrent Protection (OCP) sample and hold

operation (while COMP/SD is ~1V). When the sampling is

complete, VOUT begins the soft-start ramp.

If the COMP/SD pin is held low during power-up, that will just

delay the initialization until it is released, and the COMP/SD

voltage is above the V

Figure 2 shows a typical power-up sequence in more detail.

The initialization starts at T0, when either V

V

COMP/SD will be pulled up by an internal 20µA current

source, but the timing will not begin until the COMP/SD

exceeds the V

capacitance of the disabling device, as well as the

compensation capacitors, will determine how quickly the

20µA current source will charge the COMP/SD pin. With

typical values, it should add a small delay compared to the

soft-start times. The COMP/SD will continue to ramp to ~1V.

From t1, there is a nominal 6.8ms delay, which allows the

V

the internal bias regulator can turn on cleanly. At the same

time, the LGATE/OCSET pin is initialized, by disabling the

LGATE driver and drawing I

through R

the OCSET trip point. At t2, there is a variable time period for

the OCP sample and hold operation (0ms to 3.4ms nominal;

the longer time occurs with the higher overcurrent setting).

The sample and hold uses a digital counter and DAC to save

the voltage, so the stored value does not degrade, for as

long as the V

(OCP)” on page 7 for more details on the equations and

variables. Upon the completion of sample and hold at t3, the

GND>

POR

CC

pin to exceed 6.5V (if rising up towards 12V), so that

, or the COMP/SD pin is released (after POR). The

FIGURE 1. POR AND SOFT-START OPERATION

OCSET

CC

DISABLE

is above V

. This sets up a voltage that will represent

~4V POR

DISABLE

trip point (at t1). The external

POR

OCSET

COMP/SD (1V/DIV)

6

. See “Overcurrent Protection

trip point.

(nominal 21.5µA)

CC

V

rises above

V

OUT

CC

(2V/DIV)

(1V/DIV)

ISL6545, ISL6545A

soft-start operation is initiated, and the output voltage ramps

up between t4 and t5.

Soft-Start and Pre-Biased Outputs

Functionally, the soft-start internally ramps the reference on

the non-inverting terminal of the error amp from 0V to 0.6V in

a nominal 6.8ms The output voltage will thus follow the

ramp, from zero to final value, in the same 6.8ms (the actual

ramp seen on the V

due to some initialization timing, between t3 and t4).

The ramp is created digitally, so there will be 64 small

discrete steps. There is no simple way to change this ramp

rate externally, and it is the same for either frequency

version of the IC (300kHz or 600kHz).

After an initialization period (t3 to t4), the error amplifier

(COMP/SD pin) is enabled, and begins to regulate the

converter’s output voltage during soft-start. The oscillator’s

triangular waveform is compared to the ramping error

amplifier voltage. This generates PHASE pulses of

increasing width that charge the output capacitors. When the

internally generated soft-start voltage exceeds the reference

voltage (0.6V), the soft-start is complete, and the output

should be in regulation at the expected voltage. This method

provides a rapid and controlled output voltage rise; there is

no large inrush current charging the output capacitors. The

entire start-up sequence from POR typically takes up to

17ms; up to 10.2ms for the delay and OCP sample, and

6.8ms for the soft-start ramp.

Figure 3 shows the normal curve in blue; initialization begins

at t0, and the output ramps between t1 and t2. If the output is

pre-biased to a voltage less than the expected value, as

shown by the magenta curve, the ISL6545x will detect that

condition. Neither MOSFET will turn on until the soft-start

ramp voltage exceeds the output; V

ramping from there. If the output is pre-biased to a voltage

above the expected value, as in the red curve, neither

MOSFET will turn on until the end of the soft-start, at which

GND>

FIGURE 2. LGATE/OCSET AND SOFT-START OPERATION

0.4V

t0 t1

3.4ms

LGATE/OCSET (0.25V/DIV)

COMP/SD (0.25V/DIV)

OUT

3.4ms

will be less than the nominal time,

t2

0 - 3.4ms

OUT

t3 t4

starts seamlessly

SWITCHING

STARTS

6.8ms

LGATE

(0.5V/DIV)

V

March 3, 2011

OUT

FN6305.6

t5