ISL6545ACRZ Intersil, ISL6545ACRZ Datasheet - Page 7

ISL6545ACRZ

Manufacturer Part Number

ISL6545ACRZ

Description

IC PWM BUCK BST VM 10DFN

Manufacturer

Intersil

Datasheet

1.ISL6545ACBZ-T.pdf

(16 pages)

Specifications of ISL6545ACRZ

Pwm Type

Voltage Mode

Number Of Outputs

1

Frequency - Max

660kHz

Duty Cycle

100%

Voltage - Supply

4.5 V ~ 14.4 V

Buck

Yes

Boost

Yes

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

0°C ~ 70°C

Package / Case

10-DFN

Frequency-max

660kHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

time it will pull the output voltage down to the final value. Any

resistive load connected to the output will help pull down the

voltage (at the RC rate of the R of the load and the C of the

output capacitance).

If the V

supply that comes up after V

through its cycle, but with no output voltage ramp. When V

turns on, the output would follow the ramp of the V

close to 100% duty cycle, with COMP/SD pin >4V), from

zero up to the final expected voltage. If V

may be excessive inrush current charging the output

capacitors (only the beginning of the ramp, from zero to

V

changing the sequencing of the power supplies, or sharing

the same supply, or adding sequencing logic to the

COMP/SD pin to delay the soft-start until the V

ready (see “Input Voltage Considerations” on page 9).

If the IC is disabled after soft-start (by pulling COMP/SD pin

low), and then enabled (by releasing the COMP/SD pin),

then the full initialization (including OCP sample) will take

place. However, that there is no new OCP sampling during

overcurrent retries.

If the output is shorted to GND during soft-start, the OCP will

handle it, as described in the next section.

Overcurrent Protection (OCP)

The overcurrent function protects the converter from a

shorted output by using the lower MOSFET’s on-resistance,

r

programs the overcurrent trip level (see “Typical Application”

on page 3). This method enhances the converter’s efficiency

and reduces cost by eliminating a current sensing resistor. If

overcurrent is detected, the output immediately shuts off, it

cycles the soft-start function in a hiccup mode (2 dummy

soft-start time-outs, then up to one real one) to provide fault

protection. If the shorted condition is not removed, this cycle

will continue indefinitely.

DS(ON)

GND>

GND>

GND>

OUT

matters here). If this is not acceptable, then consider

IN

, to monitor the current. A resistor (R

V

V

V

to the upper MOSFET drain is from a different

OUT

OUT

OUT

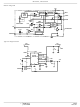

FIGURE 3. SOFT-START WITH PRE-BIAS

PRE-BIASED

OVERCHARGED

NORMAL

t0

t1

CC

7

, the soft-start would go

IN

is too fast, there

OCSET

IN

t2

supply is

IN

ISL6545, ISL6545A

)

(at

IN

Following POR (and 6.8ms delay), the ISL6545x initiates the

Overcurrent Protection sample and hold operation. The

LGATE driver is disabled to allow an internal 21.5µA current

source to develop a voltage across R

samples this voltage (which is referenced to the GND pin) at

the LGATE/OCSET pin, and holds it in a counter and DAC

combination. This sampled voltage is held internally as the

Overcurrent Set Point, for as long as power is applied, or

until a new sample is taken after coming out of a shut-down.

The actual monitoring of the lower MOSFET’s on-resistance

starts 200ns (nominal) after the edge of the internal PWM

logic signal (that creates the rising external LGATE signal).

This is done to allow the gate transition noise and ringing on

the PHASE pin to settle out before monitoring. The

monitoring ends when the internal PWM edge (and thus

LGATE) goes low. The OCP can be detected anywhere

within the above window.

If the regulator is running at high UGATE duty cycles (around

75% for 600kHz or 87% for 300kHz operation), then the

LGATE pulse width may not be wide enough for the OCP to

properly sample the r

is too narrow (or not there at all) for 3 consecutive pulses,

then the third pulse will be stretched and/or inserted to the

425ns minimum width. This allows for OCP monitoring every

third pulse under this condition. This can introduce a small

pulse-width error on the output voltage, which will be

corrected on the next pulse; and the output ripple voltage will

have an unusual 3-clock pattern, which may look like jitter.

This is not necessarily a problem; it is more of a compromise

to maintain OCP at the higher duty cycles. If the OCP is

disabled (by choosing a too-high value of R

resistor at all), then the pulse stretching feature is also

disabled. Figure 4 illustrates the LGATE pulse width

stretching, as the width gets smaller.

FIGURE 4. LGATE PULSE STRETCHING

DS(ON)

> 425 ns

= 425 ns

< 425 ns

<< 425 ns

. For those cases, if the LGATE

OCSET

. The ISL6545x

OCSET

, or no

March 3, 2011

FN6305.6